Question: Need help writing a 2 bit adder in Verilog and also finishing this test bench file. (b) Create a new Verilog source file called 'adder_2bit.v'

Need help writing a 2 bit adder in Verilog and also finishing this test bench file.

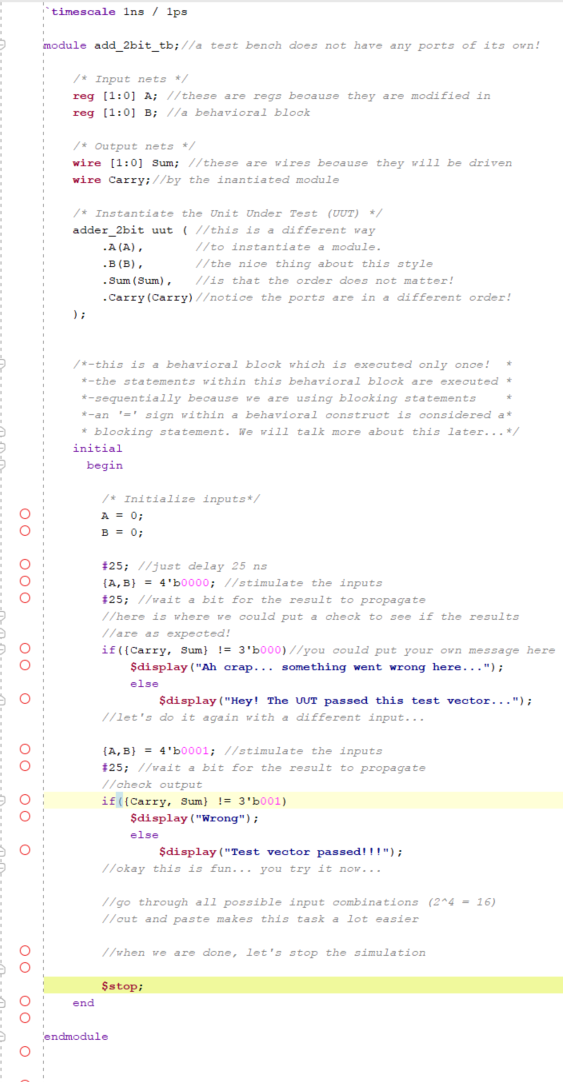

(b) Create a new Verilog source file called 'adder_2bit.v' with the following module interface: module adder_2bit (Carry, Sum, A, B); (c) To test the 2-bit adder circuit, we will use the file adder_2bit_tb. v' as a template. Copy this file from the course directory into your lab7 directory and complete the test bench code based on the hints found within the comments. timescale ins/ Ips module add_2bit_tb;//a test bench does not have any ports of its own! /* Input nets */ reg (1:0) A; //these are regs because they are modified in reg (1:0) B; Ia behavioral block * Output nets wire [1:0] Sum; //these are wires because they will be driven wire Carry; //by the inantiated module .A(A). /* Instantiate the Unit Under Test (UUT) */ adder_2bit uut (//this is a different way //to instantiate a module. .B(B). //the nice thing about this style Sum (Sum). //is that the order does not matter! .Carry (Carry) /otice the ports are in a different order! /*-this is a behavioral block which is executed only once! *-the statements within this behavioral block are executed * *-sequentially because we are using blocking statements *-an '=' sign within a behavioral construct is considered a* * blocking statement. We will talk more about this later.../ initial begin /* Initialize inputs*/ A = 0; B = 0; #25; //just delay 25 ns {A, B} = 4'50000; // stimulate the inputs #25; //wait a bit for the result to propagate //here is where we could put a check to see if the results Ware as expected! if({Carry, Sum} != 3'5000)//you could put your own message here $display ("Ah crap... something went wrong here..."); else $display("Hey! The UUT passed this test vector..."); //let's do it again with a different input... {A, B} = 4'50001; // stimulate the inputs #25; //wait a bit for the result to propagate //check output if (Carry, Sum) != 3'b001) $display ("Wrong"); else $display ("Test vector passed!!!"); //okay this is fun... you try it now... //go through all possible input combinations (2^4 = 16) //out and paste makes this task a lot easier //when we are done, let's stop the simulation $stop; end endmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts