Question: Part 2: Thought Questions Q6. Explain why the branch control signal is asserted (= 1) only when we have beq instruction, and it must be

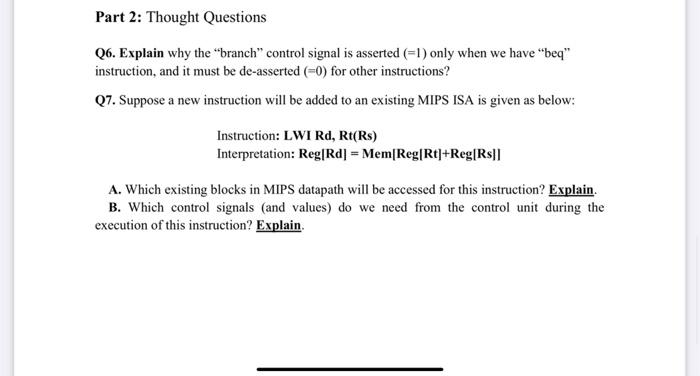

Part 2: Thought Questions Q6. Explain why the "branch" control signal is asserted (= 1) only when we have "beq" instruction, and it must be de-asserted (=0) for other instructions? Q7. Suppose a new instruction will be added to an existing MIPS ISA is given as below: Instruction: LWI Rd, Rt(Rs) Interpretation: Reg|Rd] =Mem[Reg|Rt]+Reg[R|| A. Which existing blocks in MIPS datapath will be accessed for this instruction? Explain. B. Which control signals (and values) do we need from the control unit during the execution of this instruction? Explain

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock