Question: Please can u explain the libraries, commands, architecture and test bench used in the codes listed below. VHDL code for up counter: library IEEE; use

Please can u explain the libraries, commands, architecture and test bench used in the codes listed below.

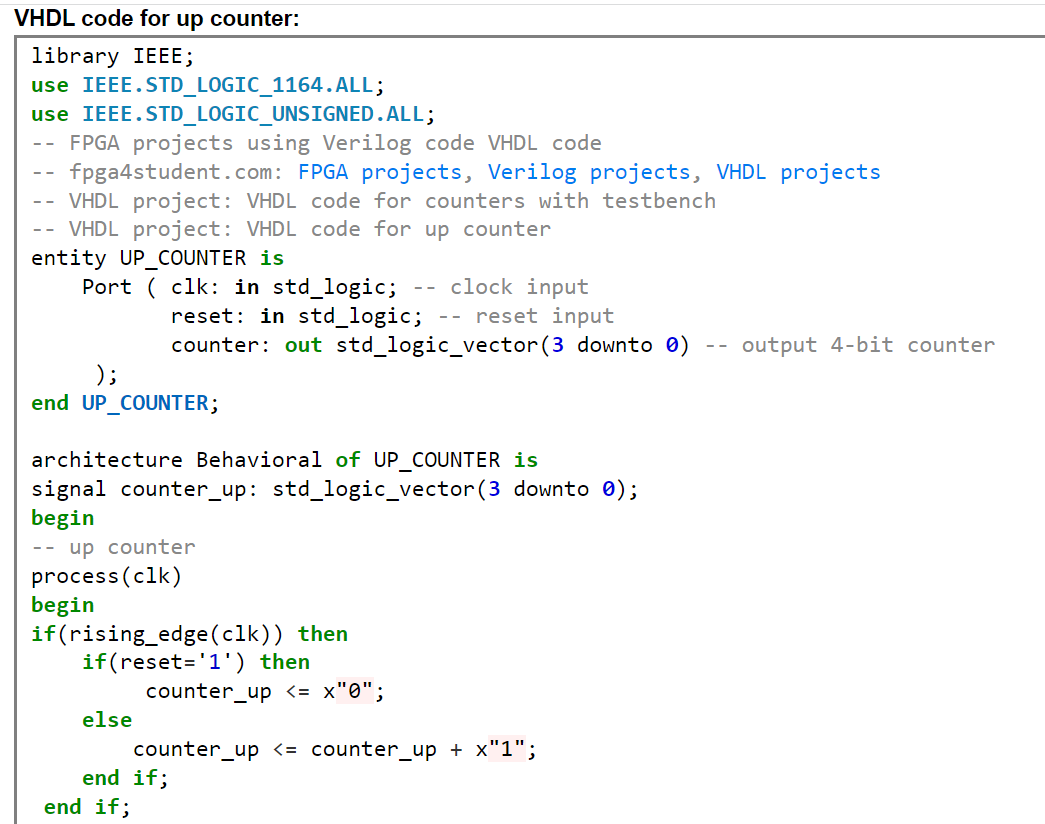

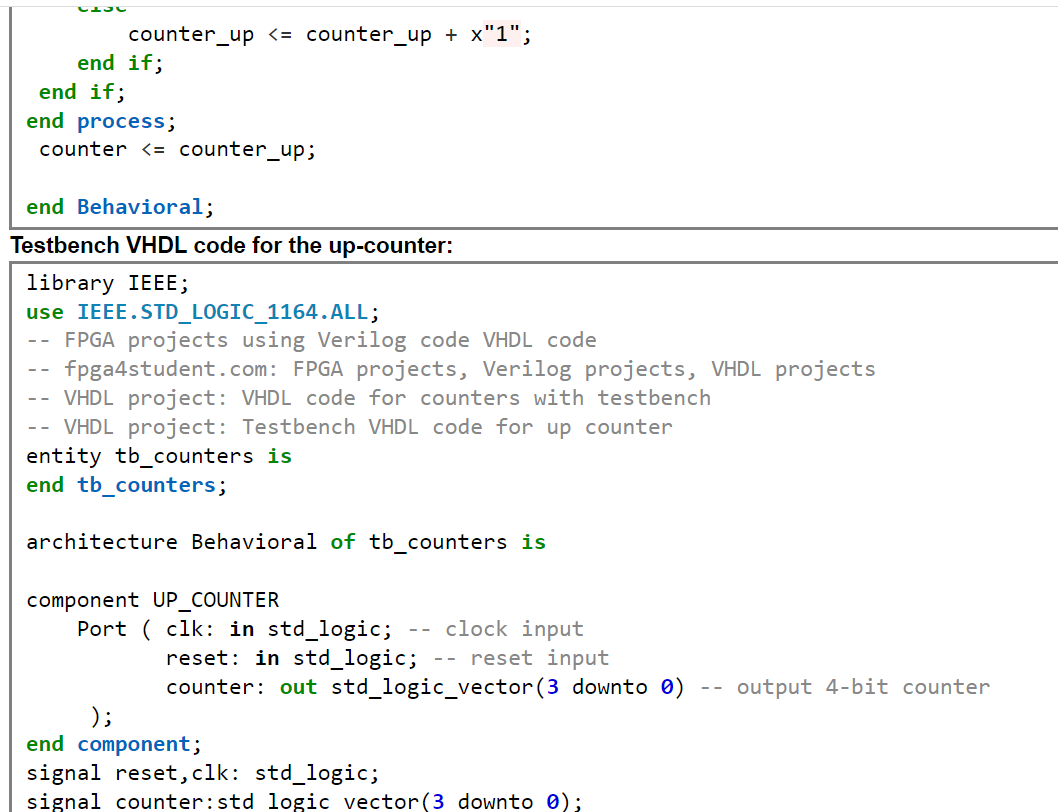

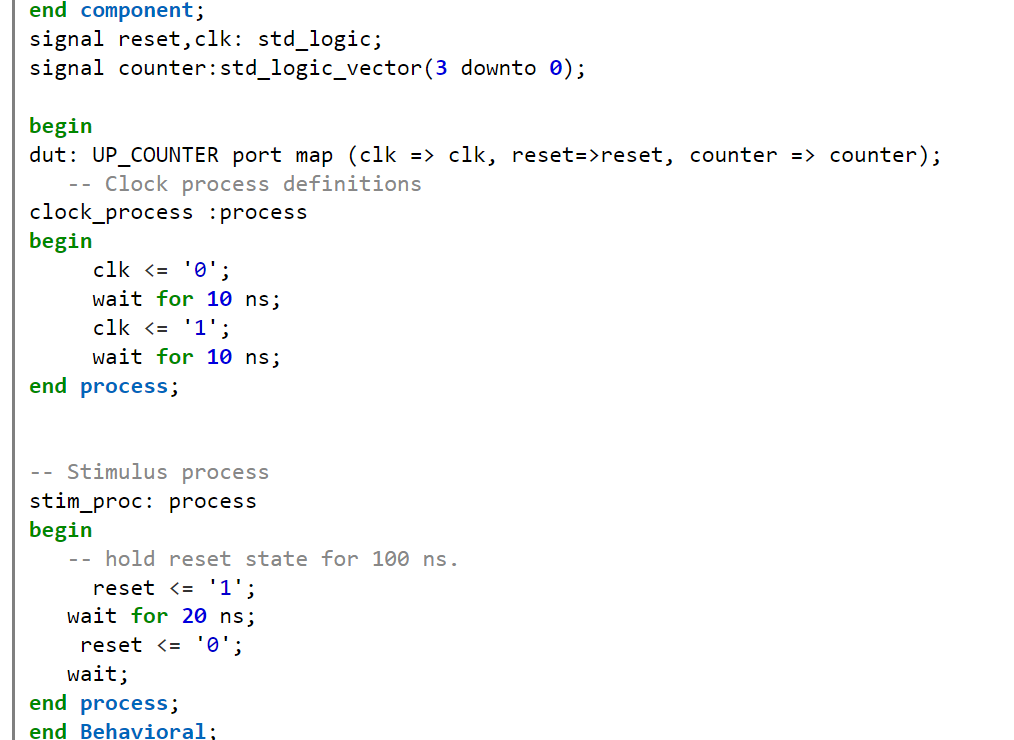

VHDL code for up counter: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; FPGA projects using Verilog code VHDL code fpga4student.com: FPGA projects, Verilog projects, VHDL projects VHDL project: VHDL code for counters with testbench -- VHDL project: VHDL code for up counter entity UP_COUNTER is Port ( clk: in std_logic; clock input reset: in std_logic; reset input counter: out std_logic_vector(3 downto 0) output 4-bit counter ); end UP_COUNTER; -- architecture Behavioral of UP_COUNTER is signal counter_up: std_logic_vector(3 downto 0); begin -- up counter process(clk) begin if(rising_edge(clk)) then if(reset='1') then counter_up clk, reset->reset, counter => counter); Clock process definitions clock_process process begin clk

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts