Question: Please help with my cs architecture homework. Will give thumbs up! this is the data from question 2: Branch X Add Add M ALU operation

Please help with my cs architecture homework. Will give thumbs up!

this is the data from question 2:

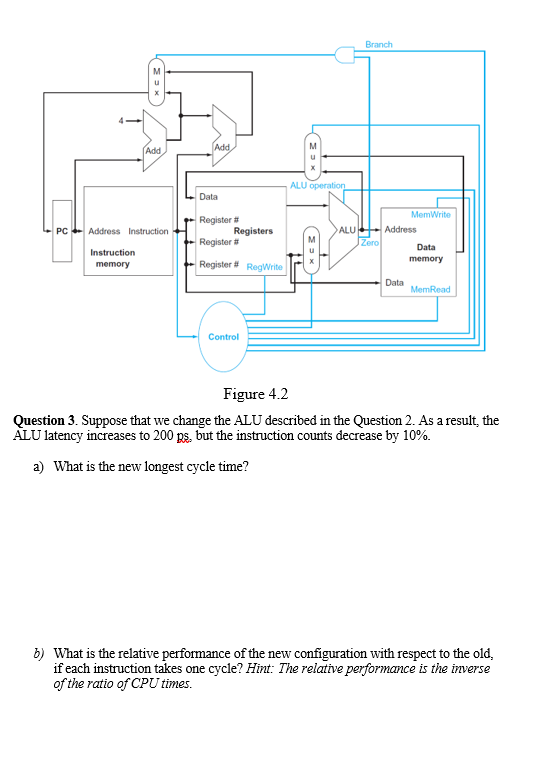

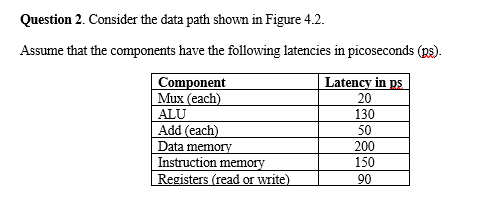

Branch X Add Add M ALU operation Data PC Address Instruction Register Registers Register ALU Zero MemWrite Address Data memory Instruction memory Register RegWrite Data MemRead Control Figure 4.2 Question 3. Suppose that we change the ALU described in the Question 2. As a result, the ALU latency increases to 200 gs. but the instruction counts decrease by 10%. a) What is the new longest cycle time? b) What is the relative performance of the new configuration with respect to the old, if each instruction takes one cycle? Hint: The relative performance is the inverse of the ratio of CPU times. Question 2. Consider the data path shown in Figure 4.2. Assume that the components have the following latencies in picoseconds (RS). Component Mux (each) ALU Add (each) Data memory Instruction memory Registers (read or write) Latency in s 20 130 50 200 150 90

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts