Question: Problem 1 (60%) Consider the following assembly program executed on a typical MIPS CPU with a 5-stage (i.e., IF stage, ID stage, EX stage, MEM

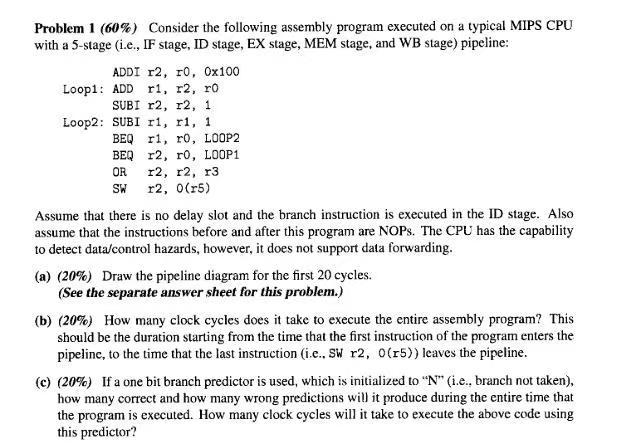

Problem 1 (60%) Consider the following assembly program executed on a typical MIPS CPU with a 5-stage (i.e., IF stage, ID stage, EX stage, MEM stage, and WB stage) pipeline: ADDI r2, ro, 0x100 Loopi: ADD r1, r2, ro SUBI r2, r2, 1 Loop2: SUBI ri, ri, 1 BEQri, ro, LOOP2 BEQ r2, ro, LOOP1 OR r2, r2, r3 SW r2, 0(r5) Assume that there is no delay slot and the branch instruction is executed in the ID stage. Also assume that the instructions before and after this program are NOPs. The CPU has the capability to detect data/control hazards, however, it does not support data forwarding. (a) (20%) Draw the pipeline diagram for the first 20 cycles. (See the separate answer sheet for this problem.) (b) (20%) How many clock cycles does it take to execute the entire assembly program? This should be the duration starting from the time that the first instruction of the program enters the pipeline, to the time that the last instruction (i.e., SW r2, 0(15)) leaves the pipeline. (c) (20%) If a one bit branch predictor is used, which is initialized to "N" (1.e., branch not taken). how many correct and how many wrong predictions will it produce during the entire time that the program is executed. How many clock cycles will it take to execute the above code using this predictor? Problem 1 (60%) Consider the following assembly program executed on a typical MIPS CPU with a 5-stage (i.e., IF stage, ID stage, EX stage, MEM stage, and WB stage) pipeline: ADDI r2, ro, 0x100 Loopi: ADD r1, r2, ro SUBI r2, r2, 1 Loop2: SUBI ri, ri, 1 BEQri, ro, LOOP2 BEQ r2, ro, LOOP1 OR r2, r2, r3 SW r2, 0(r5) Assume that there is no delay slot and the branch instruction is executed in the ID stage. Also assume that the instructions before and after this program are NOPs. The CPU has the capability to detect data/control hazards, however, it does not support data forwarding. (a) (20%) Draw the pipeline diagram for the first 20 cycles. (See the separate answer sheet for this problem.) (b) (20%) How many clock cycles does it take to execute the entire assembly program? This should be the duration starting from the time that the first instruction of the program enters the pipeline, to the time that the last instruction (i.e., SW r2, 0(15)) leaves the pipeline. (c) (20%) If a one bit branch predictor is used, which is initialized to "N" (1.e., branch not taken). how many correct and how many wrong predictions will it produce during the entire time that the program is executed. How many clock cycles will it take to execute the above code using this predictor

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts