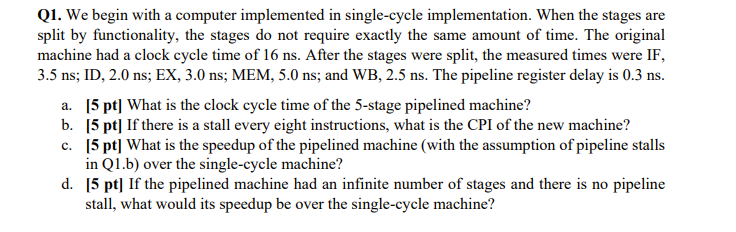

Question: Q 1 . We begin with a computer implemented in single - cycle implementation. When the stages are split by functionality, the stages do not

Q We begin with a computer implemented in singlecycle implementation. When the stages are

split by functionality, the stages do not require exactly the same amount of time. The original

machine had a clock cycle time of After the stages were split, the measured times were IF

; ID; EX; MEM, ; and WB The pipeline register delay is

a What is the clock cycle time of the stage pipelined machine?

b If there is a stall every eight instructions, what is the CPI of the new machine?

c pt What is the speedup of the pipelined machine with the assumption of pipeline stalls

in Qb over the singlecycle machine?

d pt If the pipelined machine had an infinite number of stages and there is no pipeline

stall, what would its speedup be over the singlecycle machine?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock