Question: Question #4 Consider an 8-byte, 2-way set-associative cache (using write-back with write allocation and LRU replacement policies) with 2-byte blocks and CPU has 4-bit physical

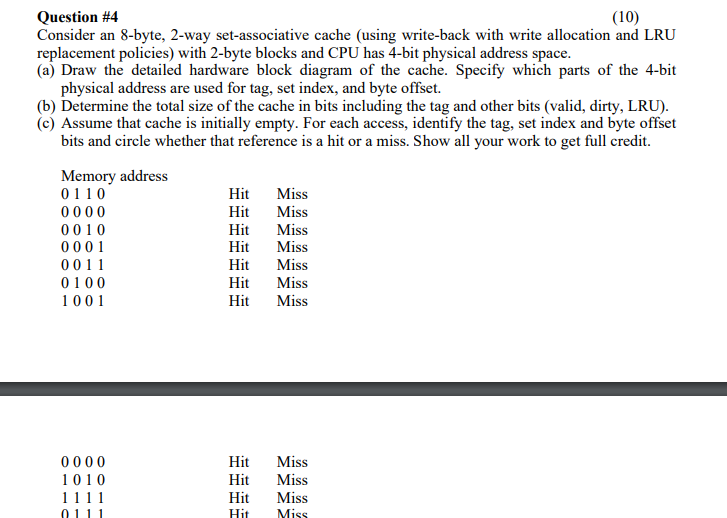

Question \#4 Consider an 8-byte, 2-way set-associative cache (using write-back with write allocation and LRU replacement policies) with 2-byte blocks and CPU has 4-bit physical address space. (a) Draw the detailed hardware block diagram of the cache. Specify which parts of the 4-bit physical address are used for tag, set index, and byte offset. (b) Determine the total size of the cache in bits including the tag and other bits (valid, dirty, LRU). (c) Assume that cache is initially empty. For each access, identify the tag, set index and byte offset bits and circle whether that reference is a hit or a miss. Show all your work to get full credit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts