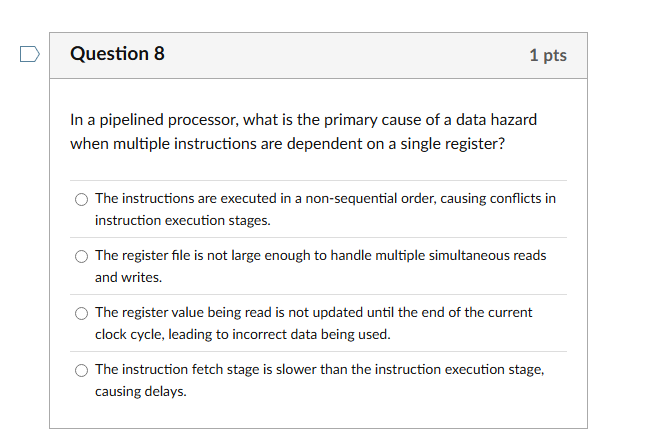

Question: Question 8 In a pipelined processor, what is the primary cause of a data hazard when multiple instructions are dependent on a single register? The

Question

In a pipelined processor, what is the primary cause of a data hazard when multiple instructions are dependent on a single register?

The instructions are executed in a nonsequential order, causing conflicts in instruction execution stages.

The register file is not large enough to handle multiple simultaneous reads and writes.

The register value being read is not updated until the end of the current clock cycle, leading to incorrect data being used.

The instruction fetch stage is slower than the instruction execution stage, causing delays.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock