Question: Questions No . 1 The given datapath circuit represents a shift - and - add multiplier design with three registers of sizes 2 n ,

Questions No

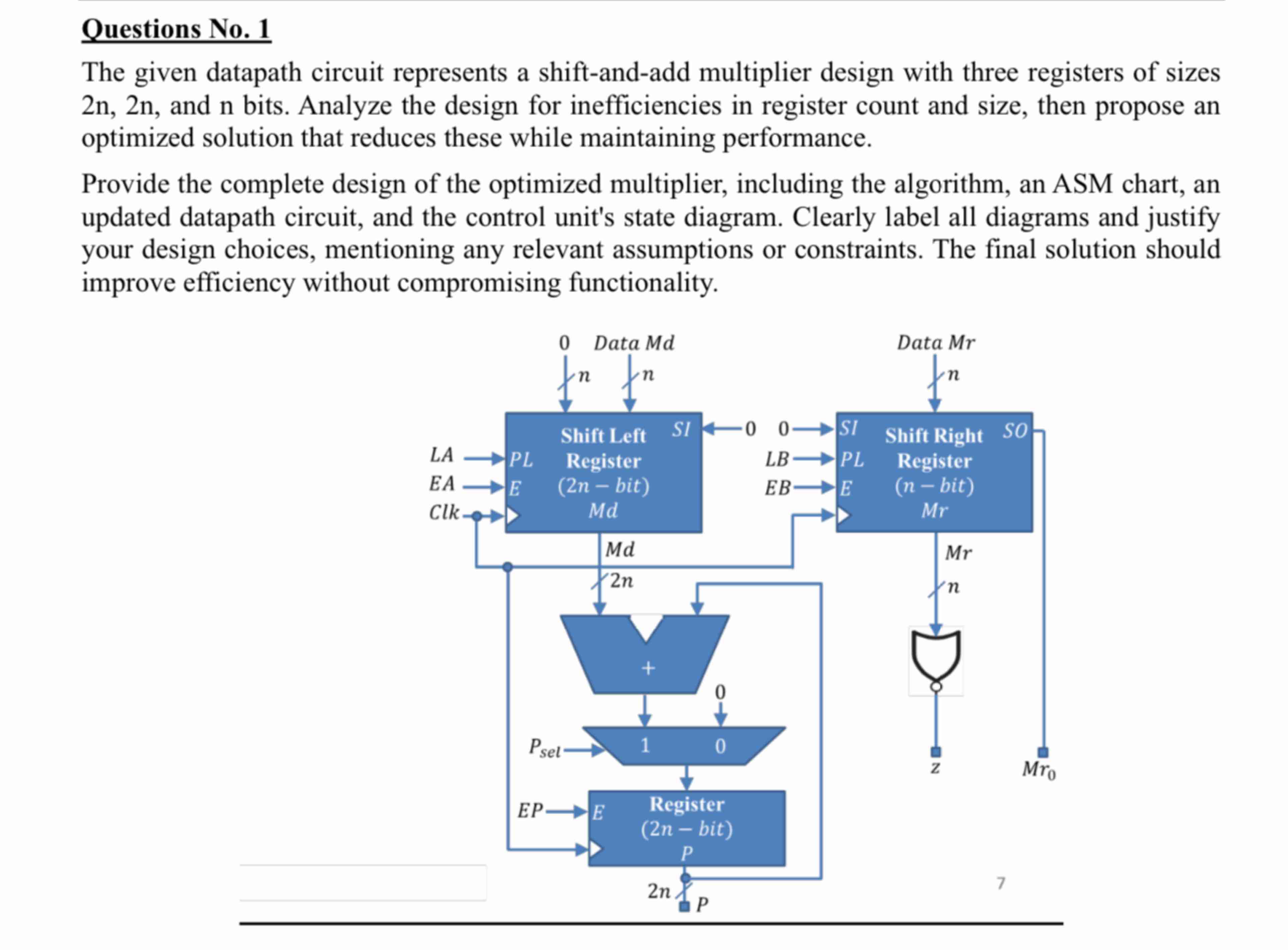

The given datapath circuit represents a shiftandadd multiplier design with three registers of sizes

nn and n bits. Analyze the design for inefficiencies in register count and size, then propose an

optimized solution that reduces these while maintaining performance.

Provide the complete design of the optimized multiplier, including the algorithm, an ASM chart, an

updated datapath circuit, and the control unit's state diagram. Clearly label all diagrams and justify

your design choices, mentioning any relevant assumptions or constraints. The final solution shouldimprove efficiency without compromising functionality.

Note: product register remain n bit while the md register is n bit now provide optimize solution

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock