Question: SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog

SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog SystemVerilog

Also,

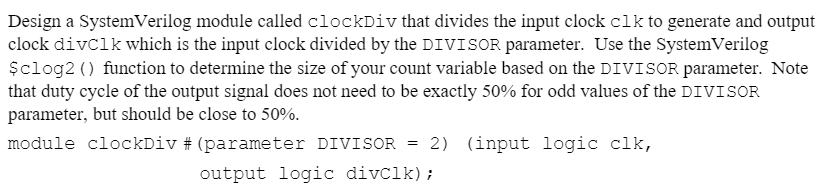

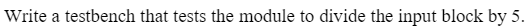

Design a SystemVerilog module called clockDiv that divides the input clock clk to generate and output clock divclk which is the input clock divided by the DIVISOR parameter. Use the SystemVerilog $clog2 () function to determine the size of your count variable based on the DIVISOR parameter. Note that duty cycle of the output signal does not need to be exactly 50% for odd values of the DIVISOR parameter, but should be close to 50%. module clockDiv # (parameter DIVISOR = 2) (input logic clk, output logic divcik); Write a testbench that tests the module to divide the input block by 5. Design a SystemVerilog module called clockDiv that divides the input clock clk to generate and output clock divclk which is the input clock divided by the DIVISOR parameter. Use the SystemVerilog $clog2 () function to determine the size of your count variable based on the DIVISOR parameter. Note that duty cycle of the output signal does not need to be exactly 50% for odd values of the DIVISOR parameter, but should be close to 50%. module clockDiv # (parameter DIVISOR = 2) (input logic clk, output logic divcik); Write a testbench that tests the module to divide the input block by 5

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts