Question: Thanks 3- An implementation of a processor's datapath has the following latencies: Regs D-Mem Control 90ps 250 ps PC I-MemAddMuxALU 20 ps 200 ps 70

Thanks

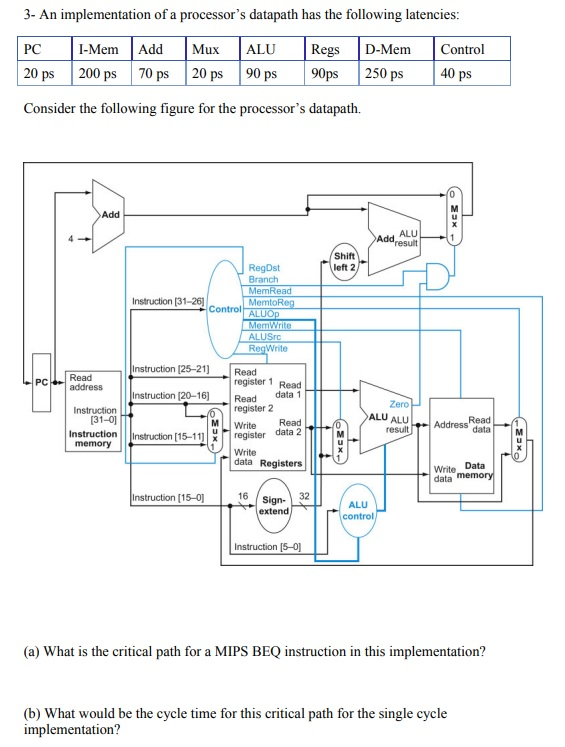

3- An implementation of a processor's datapath has the following latencies: Regs D-Mem Control 90ps 250 ps PC I-MemAddMuxALU 20 ps 200 ps 70 ps 2 ps 90 ps 40 ps Consider the following figure for the processor's datapath. MI Add Add Shift left 2 emRea MemtoRe Instruction [31-26 Control 25-21] Read register 1 Read Read data 1 Read PRead Zero register 2 31-0 ALU ALUAddress dataM M Write data2 Instruction 15-11 Y U register Write data Registers Write Data 16 Instruction [15-0] Sign32 control Instruction I5-o (a) What is the critical path for a MIPS BEQ instruction in this implementation? (b) What would be the cycle time for this critical path for the single cycle implementation? 3- An implementation of a processor's datapath has the following latencies: Regs D-Mem Control 90ps 250 ps PC I-MemAddMuxALU 20 ps 200 ps 70 ps 2 ps 90 ps 40 ps Consider the following figure for the processor's datapath. MI Add Add Shift left 2 emRea MemtoRe Instruction [31-26 Control 25-21] Read register 1 Read Read data 1 Read PRead Zero register 2 31-0 ALU ALUAddress dataM M Write data2 Instruction 15-11 Y U register Write data Registers Write Data 16 Instruction [15-0] Sign32 control Instruction I5-o (a) What is the critical path for a MIPS BEQ instruction in this implementation? (b) What would be the cycle time for this critical path for the single cycle implementation

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts