Question: The following program is running on the 5-stage pipelined processor shown in class. Assume that all registers are initialized to 0. lw $r1, 8($r5) lw

The following program is running on the 5-stage pipelined processor shown in class. Assume that all registers are initialized to 0.

lw $r1, 8($r5)

lw $r2, 16($r4)

sub $r7, $r1, $r2

beq $r9, $r7, label

add $r1, $r10, $r11

sw $r6, 0($r1)

label:

lw $r12, 4($r3)

and $r4, $r12 $r7

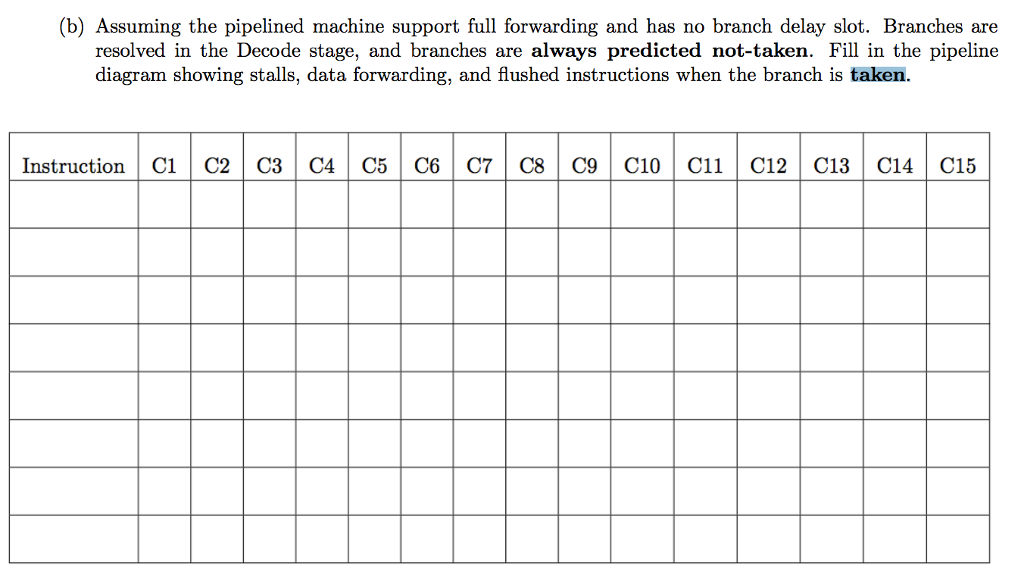

(b) Assuming the pipelined machine support full forwarding and has no branch delay slot. Branches are resolved in the Decode stage, and branches are always predicted not-taken. Fill in the pipeline diagram showing stalls, data forwarding, and flushed instructions when the branch is taken. Instruction C1 C2 C3 C4 C5C6 C7 C8 C9 C10 C11 C12 C13C14 C15

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts