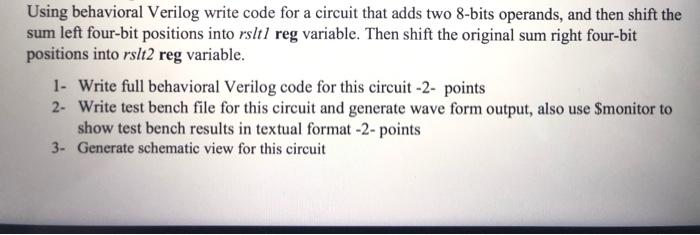

Question: Using behavioral Verilog write code for a circuit that adds two 8-bits operands, and then shift the sum left four-bit positions into rsltl reg variable.

Using behavioral Verilog write code for a circuit that adds two 8-bits operands, and then shift the sum left four-bit positions into rsltl reg variable. Then shift the original sum right four-bit positions into rslt2 reg variable. 1. Write full behavioral Verilog code for this circuit -2- points 2- Write test bench file for this circuit and generate wave form output, also use $monitor to show test bench results in textual format -2- points 3- Generate schematic view for this circuit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts