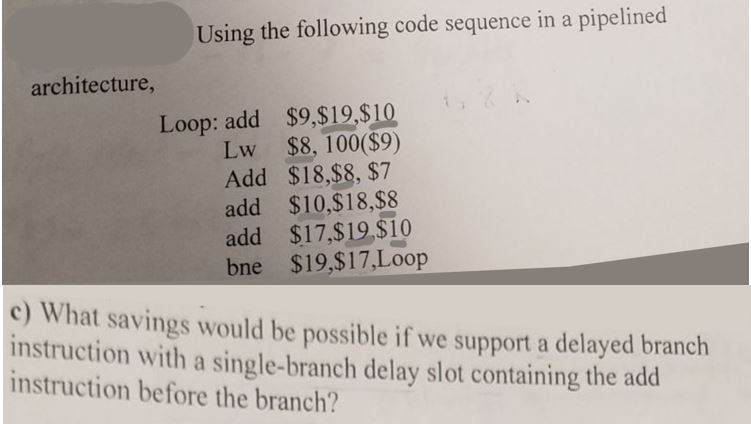

Question: Using the following code sequence in a pipelined architecture, Loop: add $9,$19,$10 Lw $8, 100($9) Add $18,S8, $7 add $10,S18,S8 add $17,S19,S10 bne $19,$17,Loop c)

Using the following code sequence in a pipelined architecture, Loop: add $9,$19,$10 Lw $8, 100($9) Add $18,S8, $7 add $10,S18,S8 add $17,S19,S10 bne $19,$17,Loop c) What savings would be possible if we support a delayed branch instruction with a single-branch delay slot containing the add instruction before the branch

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts