Question: virtual memory uses a page table to track the mapping of virtual addresses to physical addresses. This exercise shows how this table must be updated

virtual memory uses a page table to track the mapping of virtual addresses to physical addresses. This exercise shows how this table must be updated as addresses are accessed. The following data constitute a stream of virtual byte addresses as seen on a system.

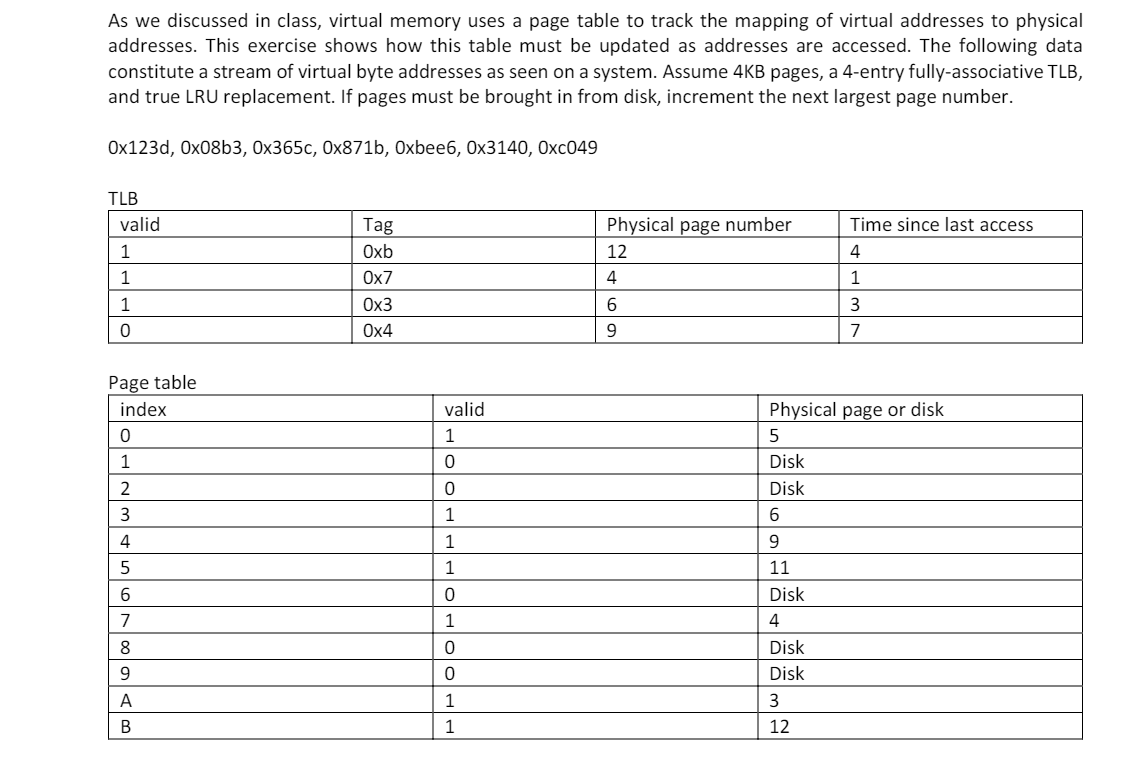

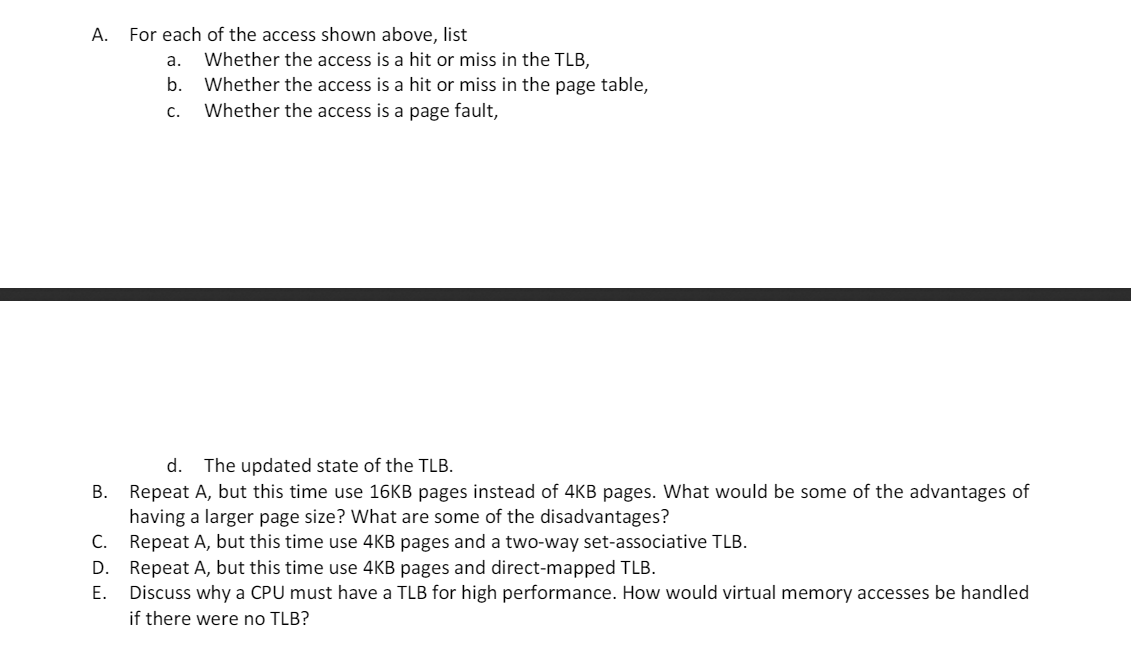

As we discussed in class, virtual memory uses a page table to track the mapping of virtual addresses to physical addresses. This exercise shows how this table must be updated as addresses are accessed. The following data constitute a stream of virtual byte addresses as seen on a system. Assume 4KB pages, a 4-entry fully-associative TLB, and true LRU replacement. If pages must be brought in from disk, increment the next largest page number. Ox123d, Ox08b3, 0x365c, 0x871b, Oxbee6, 0x3140, 0xc049 TLB valid 1 Time since last access 4 Tag Oxb Ox7 Ox3 Ox4 Physical page number 12 4 6 1 1 3 1 0 9 7 Page table index valid 0 1 2 Physical page or disk 5 Disk Disk 6 9 11 Disk 3 4 5 |10|0|1|1|1|0|1000 11 6 7 4 8 9 Disk Disk 3 12 A B A. a. For each of the access shown above, list Whether the access is a hit or miss in the TLB, b. Whether the access is a hit or miss in the page table, Whether the access is a page fault, C. d. The updated state of the TLB. B. Repeat A, but this time use 16KB pages instead of 4KB pages. What would be some of the advantages of having a larger page size? What are some of the disadvantages? C. Repeat A, but this time use 4KB pages and a two-way set-associative TLB. D. Repeat A, but this time use 4KB pages and direct-mapped TLB. E. Discuss why a CPU must have a TLB for high performance. How would virtual memory accesses be handled if there were no TLB? As we discussed in class, virtual memory uses a page table to track the mapping of virtual addresses to physical addresses. This exercise shows how this table must be updated as addresses are accessed. The following data constitute a stream of virtual byte addresses as seen on a system. Assume 4KB pages, a 4-entry fully-associative TLB, and true LRU replacement. If pages must be brought in from disk, increment the next largest page number. Ox123d, Ox08b3, 0x365c, 0x871b, Oxbee6, 0x3140, 0xc049 TLB valid 1 Time since last access 4 Tag Oxb Ox7 Ox3 Ox4 Physical page number 12 4 6 1 1 3 1 0 9 7 Page table index valid 0 1 2 Physical page or disk 5 Disk Disk 6 9 11 Disk 3 4 5 |10|0|1|1|1|0|1000 11 6 7 4 8 9 Disk Disk 3 12 A B A. a. For each of the access shown above, list Whether the access is a hit or miss in the TLB, b. Whether the access is a hit or miss in the page table, Whether the access is a page fault, C. d. The updated state of the TLB. B. Repeat A, but this time use 16KB pages instead of 4KB pages. What would be some of the advantages of having a larger page size? What are some of the disadvantages? C. Repeat A, but this time use 4KB pages and a two-way set-associative TLB. D. Repeat A, but this time use 4KB pages and direct-mapped TLB. E. Discuss why a CPU must have a TLB for high performance. How would virtual memory accesses be handled if there were no TLB

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts