Question: We have a 2-way set associative cache with data block size of 32 bytes. The physical address width is 33 bits. For each block there

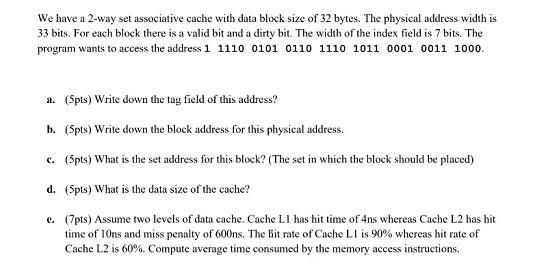

We have a 2-way set associative cache with data block size of 32 bytes. The physical address width is 33 bits. For each block there is a valid bit and a dirty bit. The width of the index field is 7 bits. The program wants to access the address 111100101011011101011000100111000. a. (Spts) Write down the tag field of this address? b. (5pts) Write down the block address for this physical address. c. (5pts) What is the set address for this block? (The set in which the block should be placed) d. (5pts) What is the data size of the cache? e. (7pts) Assume two levels of data cache. Cache LI has hit time of 4 ns whereas Cache L2 has hit time of 10ns and miss penalty of 600ns. The Git rate of Cache LI is 90% whereas hit rate of Cache L2 is 60%. Compute average time consumed by the memory access instructions

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts