Question: What would be the clock cycle period for this processor? Assume that PC register and AND gate dont take any latency (i.e. PC value is

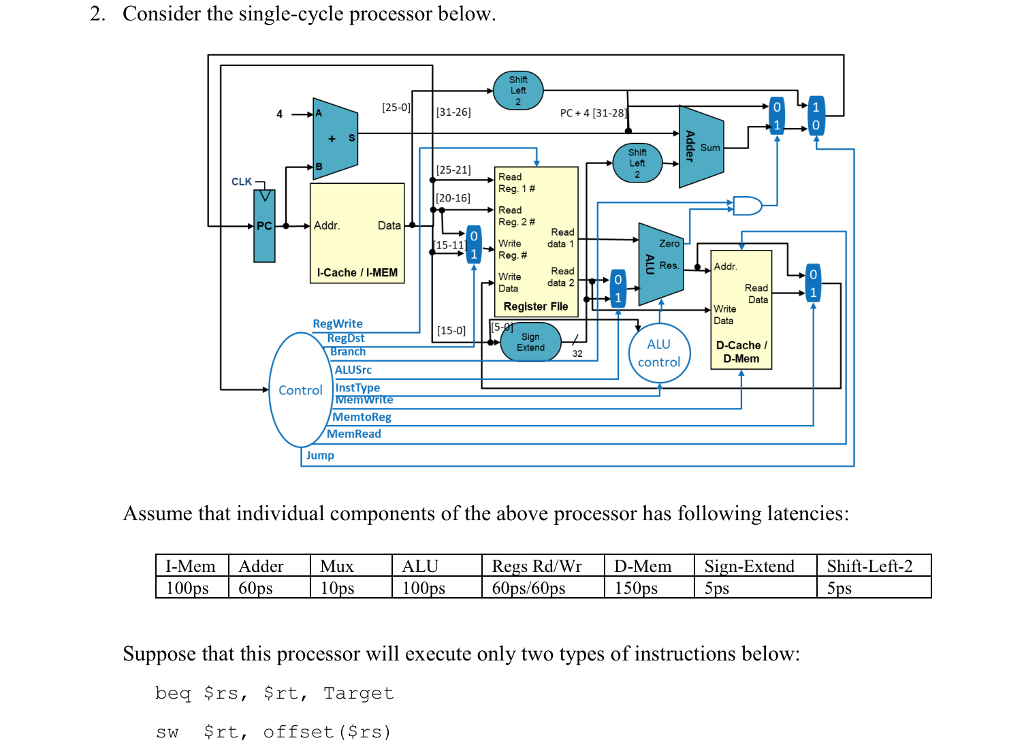

What would be the clock cycle period for this processor? Assume that PC register and AND gate dont take any latency (i.e. PC value is passed to I-Mem immediately after clock cycle begins). For the sw, a full latency of D-Mem should be also considered.

2. Consider the single-cycle processor below. Shift Left [25-01 (31-26] PC + 4 [31-28 Adder [25-21) Read Reg. 1# (20-16] PC Addr. Data ALU I-Cache/I-MEM Addr. Read Reg. 2# Read Write data 1 Reg. # Write Read Data data 2 Register File ||5-T Sign Extend HO Read Data Write Data ALU control D-Cache/ D-Mem RegWrite RegDst Branch ALUSrc Control InstType Memwrite MemtoReg MemRead Jump Assume that individual components of the above processor has following latencies: I-Mem | 100ps Adder 60ps Mux 10ps A LU 100ps Regs Rd/Wr 60ps/60ps D-Mem 150ps Sign-Extend 5ps Shift-Left-2 5ps Suppose that this processor will execute only two types of instructions below: beq $rs, $rt, Target sw $rt, offset ($rs) 2. Consider the single-cycle processor below. Shift Left [25-01 (31-26] PC + 4 [31-28 Adder [25-21) Read Reg. 1# (20-16] PC Addr. Data ALU I-Cache/I-MEM Addr. Read Reg. 2# Read Write data 1 Reg. # Write Read Data data 2 Register File ||5-T Sign Extend HO Read Data Write Data ALU control D-Cache/ D-Mem RegWrite RegDst Branch ALUSrc Control InstType Memwrite MemtoReg MemRead Jump Assume that individual components of the above processor has following latencies: I-Mem | 100ps Adder 60ps Mux 10ps A LU 100ps Regs Rd/Wr 60ps/60ps D-Mem 150ps Sign-Extend 5ps Shift-Left-2 5ps Suppose that this processor will execute only two types of instructions below: beq $rs, $rt, Target sw $rt, offset ($rs)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts