Question: When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following three problems, assume

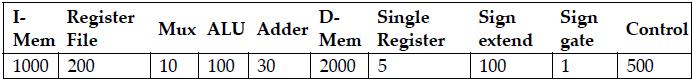

When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following three problems, assume that we are beginning with the datapath from Figure 4.21, the latencies from Exercise 4.7, and the following costs:

Suppose doubling the number of general purpose registers from 32 to 64 would reduce the number of lw and sw instruction executed by 12%, but increase the latency of the register file from 150 ps to 160 ps and double the cost from 200 to 400.

1. What is the speedup achieved by adding this improvement?

2. Compare the change in performance to the change in cost.

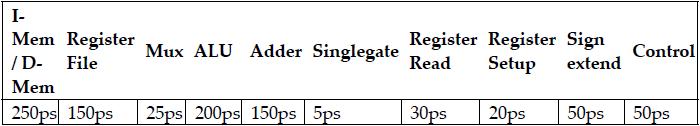

Data from Exercise 4.7

Problems in this exercise assume that the logic blocks used to implement a processor’s datapath have the following latencies:

“Register read” is the time needed after the rising clock edge for the new register value to appear on the output. This value applies to the PC only. “Register setup” is the amount of time a register’s data input must be stable before the rising edge of the clock. This value applies to both the PC and Register File.

1. What is the latency of an R-type instruction (i.e., how long must the clock period be to ensure that this instruction works correctly)?

2. What is the latency of lw? (Check your answer carefully. Many students place extra muxes on the critical path.)

3. What is the latency of sw? (Check your answer carefully. Many students place extra muxes on the critical path.)

4. What is the latency of beq?

5. What is the latency of an arithmetic, logical, or shift

I-type (non-load) instruction?

6. What is the minimum clock period for this CPU?

Figure 4.21

![PC Add Read address Instruction (31-01 Instruction [31-26] Instruction [25-21] Instruction [20-16]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1703/7/6/8/476658d719c50eb01703768474996.jpg)

I- Register Mem File 1000 200 Mux ALU Adder 10 100 30 D- Single Mem Register 2000 5 Sign Sign extend gate 100 1 Control 500

Step by Step Solution

3.31 Rating (148 Votes )

There are 3 Steps involved in it

To proceed with the analysis we need to ascertain two main metrics of performance the execution time and the cost From these metrics we can determine the speedup and compare it to the change in cost a... View full answer

Get step-by-step solutions from verified subject matter experts