Question: 2. Consider the single-cycle processor below. 2. Consider the single-cycle processor below Shift 31-26] PC 4 131-28 Shift 25-21Read CLK Reg. 1# 20-16] Addr Data

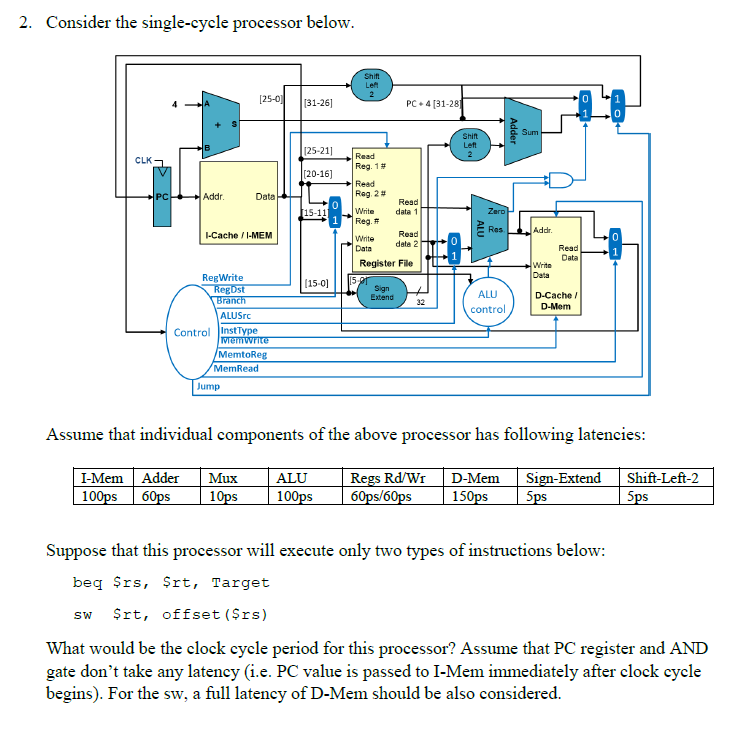

2. Consider the single-cycle processor below.

2. Consider the single-cycle processor below Shift 31-26] PC 4 131-28 Shift 25-21Read CLK Reg. 1# 20-16] Addr Data Reg 2# Writedata 1 Reg. Res WniteRead Data date 2 I-Cache I-MEM Read Data Register File RegWrite 15-05 ALU control Extend D-Cache / 32 ALUSrc Control InstType MemtoReg MemRead Assume that individual components of the above processor has following latencies I-MemAdderMux Regs Rd/Wr D-Mem Sign-Extend Shift-Left-2 15 Suppose that this processor will execute only two types of instructions below: beq Srs, Srt, Target sw $rt, offset (Srs) What would be the clock cycle period for this processor? Assume that PC register and AND gate don't take any latency (i.e. PC value is passed to I-Mem immediately after clock cycle begins). For the sw, a full latency of D-Mem should be also considered. 2. Consider the single-cycle processor below Shift 31-26] PC 4 131-28 Shift 25-21Read CLK Reg. 1# 20-16] Addr Data Reg 2# Writedata 1 Reg. Res WniteRead Data date 2 I-Cache I-MEM Read Data Register File RegWrite 15-05 ALU control Extend D-Cache / 32 ALUSrc Control InstType MemtoReg MemRead Assume that individual components of the above processor has following latencies I-MemAdderMux Regs Rd/Wr D-Mem Sign-Extend Shift-Left-2 15 Suppose that this processor will execute only two types of instructions below: beq Srs, Srt, Target sw $rt, offset (Srs) What would be the clock cycle period for this processor? Assume that PC register and AND gate don't take any latency (i.e. PC value is passed to I-Mem immediately after clock cycle begins). For the sw, a full latency of D-Mem should be also considered

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts