Question: Why does my testbench waveform have a delay and the values are off? Here is the design file: module line ( input rst _ n

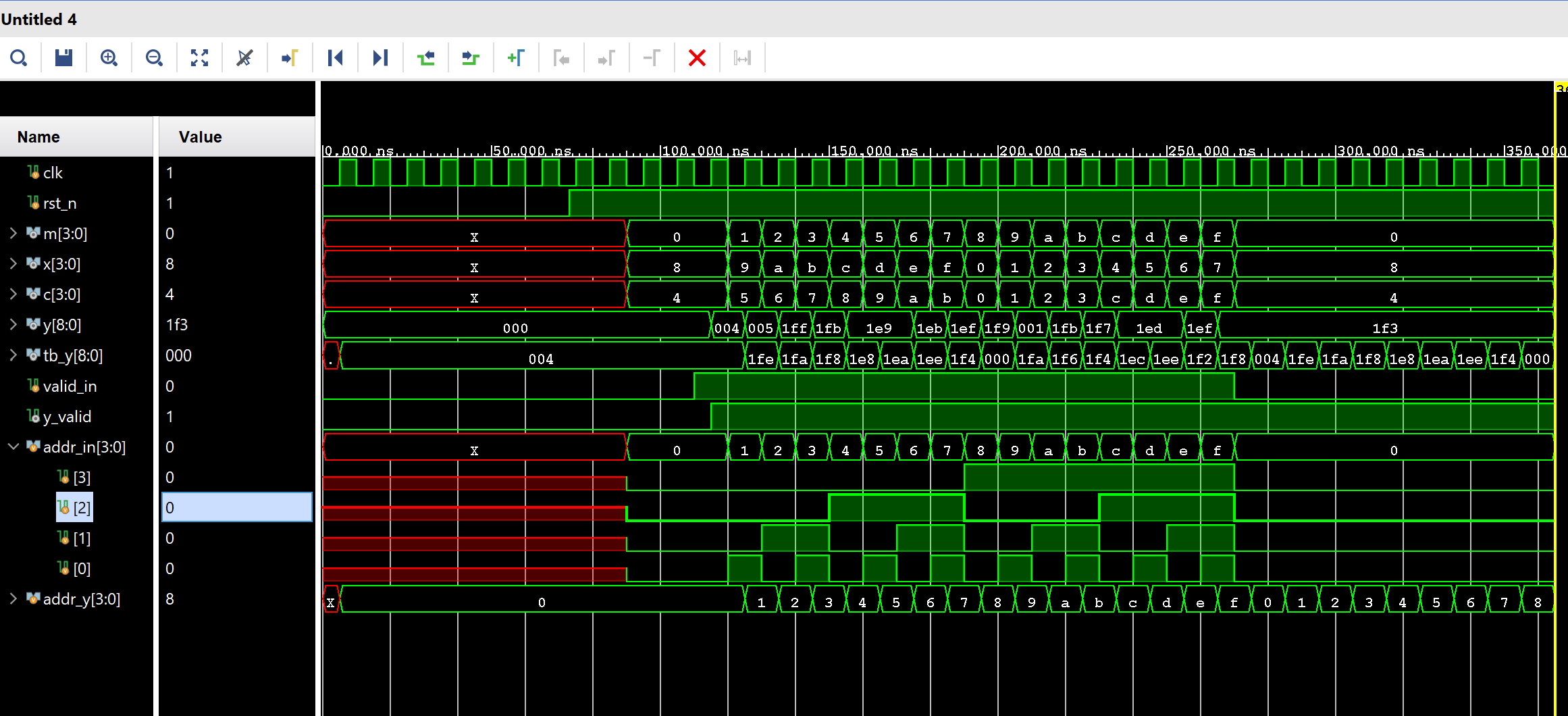

Why does my testbench waveform have a delay and the values are off?

Here is the design file:

module line

input rstn Active low reset

input clk Clock

input signed : m Signed input m

input signed : x Signed input x

input signed : c Signed input c

input validin Inputs valid

output reg signed : y Signed output y

output reg yvalid Y valid, driven by design

;

reg signed : product; Intermediate result for mx

Stage : Calculate the product mx

always @posedge clk or negedge rstn begin

if rstn begin

product b;

end else if validin begin

product m x;

end

end

Stage : Calculate the sum product c

always @posedge clk or negedge rstn begin

if rstn begin

y b;

yvalid b;

end else if validin begin

y product c;

yvalid b;

end

end

endmodule

Here is the testbench file which was provided by the professor should not be modified:

module tbline

;

reg clk;

reg rstn;

wire signed : m;

wire signed : x;

wire signed : c;

wire signed : y;

wire signed : tby;

reg validin;

wire yvalid;

reg : addrin addry;

line dut ;

rom #addrwidth datawidth initfilemdat"

mmem

addraddrin

data m

;

rom #addrwidth datawidth initfilexdat"

xmem

addraddrin

data x

;

rom #addrwidth datawidth initfilecdat"

cmem

addraddrin

data c

;

rom #addrwidth datawidth initfileydat"

ymem

addraddry

data tby

;

always # clk ~clk;

integer filehandle;

initial

begin

filehandle $fopenoutputtxtw;

clk ;

rstn h;

validin ;

# rstn h;

#;

addrin h;

#;

validin ;

for integer i ; i ; i i

begin

#;

assert y tby;

addrin addrin ;

end

validin ;

#;

$fclosefilehandle;

end

alwaysff @ posedge clk

begin

if rstn

begin

addry #h;

end

else if yvalid

begin

$fwritefilehandle, b

y;

assert y tby

else $fataly not equal to tby;

addry # addry ;

end

end

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock