Question: X z W In the circuit below, setup time, hold time, propagation delay and contamination delay of flip-flops (R1, R2) are 1 ns, 0.7 ns,

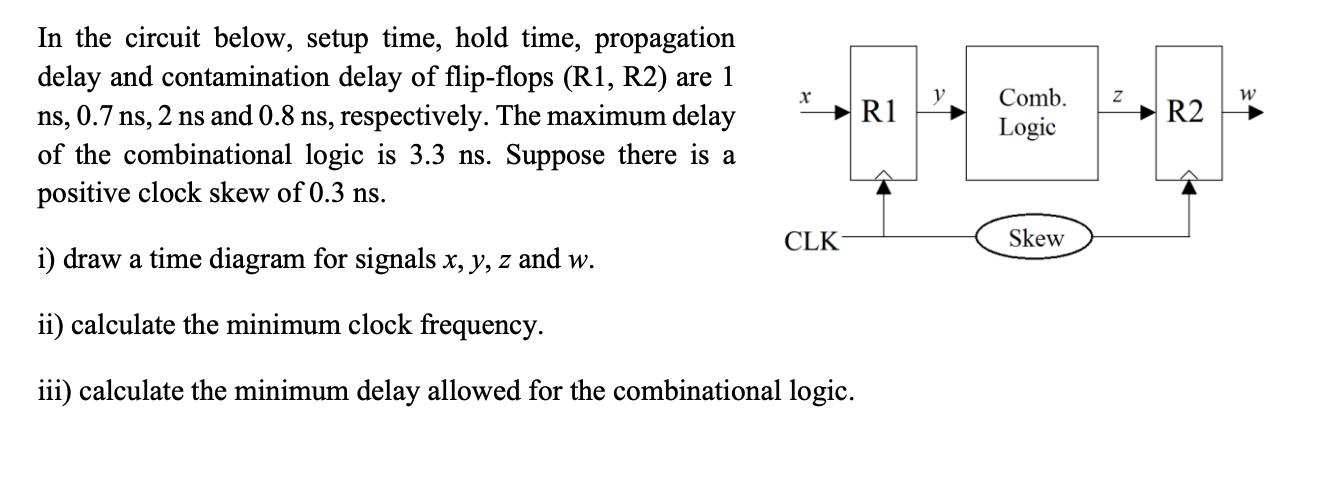

X z W In the circuit below, setup time, hold time, propagation delay and contamination delay of flip-flops (R1, R2) are 1 ns, 0.7 ns, 2 ns and 0.8 ns, respectively. The maximum delay of the combinational logic is 3.3 ns. Suppose there is a positive clock skew of 0.3 ns. R1 Comb. Logic R2 CLK Skew i) draw a time diagram for signals x, y, z and w. ii) calculate the minimum clock frequency. iii) calculate the minimum delay allowed for the combinational logic. X z W In the circuit below, setup time, hold time, propagation delay and contamination delay of flip-flops (R1, R2) are 1 ns, 0.7 ns, 2 ns and 0.8 ns, respectively. The maximum delay of the combinational logic is 3.3 ns. Suppose there is a positive clock skew of 0.3 ns. R1 Comb. Logic R2 CLK Skew i) draw a time diagram for signals x, y, z and w. ii) calculate the minimum clock frequency. iii) calculate the minimum delay allowed for the combinational logic

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts