Question: This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined datapaths

This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined datapaths from Figure 4.53. These problems assume that, of all the instructions executed in a processor, the following fraction of these instructions has a particular type of RAW data dependence. The type of RAW data dependence is identified by the stage that produces the result (EX or MEM) and the next instruction that consumes the result (1st instruction that follows the one that produces the result, 2nd instruction that follows, or both). We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle, so “EX to 3rd” and “MEM to 3rd” dependences are not counted because they cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards.

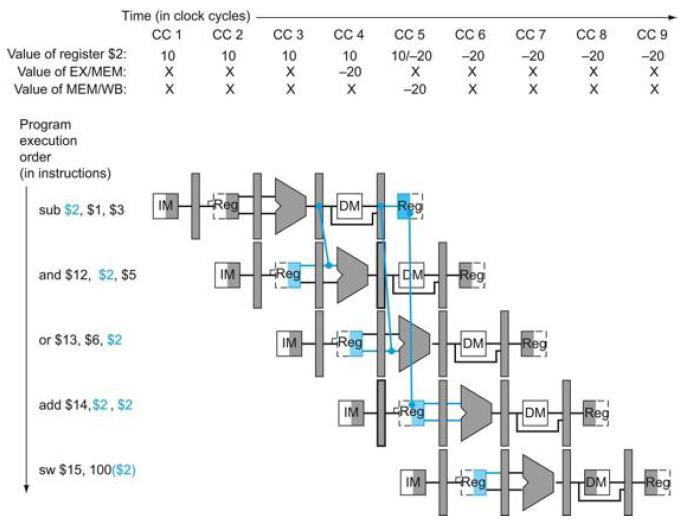

Figure 4.53

Time (in clock cycles) CC1CC 2 Value of register $2: Value of EX/MEM: Value of MEM/WB: Program execution order (in instructions) sub $2, $1, $3 and $12, $2, $5 or $13, $6. $2 add $14,$2,$2 sw $15, 100($2) 10 X X IM 10 x X Reg IM CC 3 10 X X IM CC 4 10 -20 X DM Reg IM CC 5 10/-20 x -20 Reg CC 6 -20 HOM- Reg IM xx DM Reg CC 7. -20 x X Reg CC B -20 x X TDM Reg DM CC 9 -20 x x Reg

Step by Step Solution

3.35 Rating (158 Votes )

There are 3 Steps involved in it

Understand and analyze the RAW hazards and determine when forwarding is required to maintain CPI 1 i... View full answer

Get step-by-step solutions from verified subject matter experts