Question: If an overflow exception occurs once for every 100,000 instructions executed, what is the overall speedup if we move overflow checking into the MEM stage?

If an overflow exception occurs once for every 100,000 instructions executed, what is the overall speedup if we move overflow checking into the MEM stage? Assume that this change reduces EX latency by 30ns and that the IPC achieved by the pipelined processor is 1 when there are no exceptions.

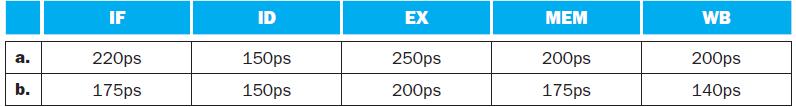

The remaining three problems in this exercise assume that pipeline stages have the following latencies:

a. b. IF 220ps 175ps ID 150ps 150ps EX 250ps 200ps MEM 200ps 175ps WB 200ps 140ps

Step by Step Solution

3.50 Rating (160 Votes )

There are 3 Steps involved in it

Calculate the CPI without overflow checking CPI IF ID EX MEM WB IPC CPI 220ps 150ps 250ps 200ps 200p... View full answer

Get step-by-step solutions from verified subject matter experts