If it costs $1 to reduce the latency of a single component of the datapath by 1ps,

Question:

If it costs $1 to reduce the latency of a single component of the datapath by 1ps, what would it cost to reduce the clock cycle time by 20% in the single-cycle and in the pipelined design?

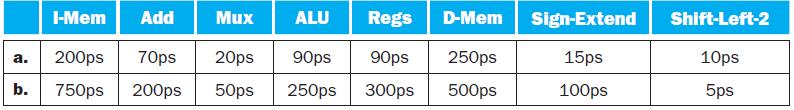

The remaining three problems in this exercise assume that components of the datapath have the following latencies:

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy

Question Posted: