Question: What is the speedup of going from a 1-issue processor to a 2-issue processor from Figure 4.69? Use your code from 4.28.1 for both 1-issue

What is the speedup of going from a 1-issue processor to a 2-issue processor from Figure 4.69? Use your code from 4.28.1 for both 1-issue and 2-issue, and assume that 1,000,000 iterations of the loop are executed. As in 4.28.2, assume that the processor has perfect branch predictions, and that a 2-issue processor can fetch any two instructions in the same cycle.

Exercise 4.28.2

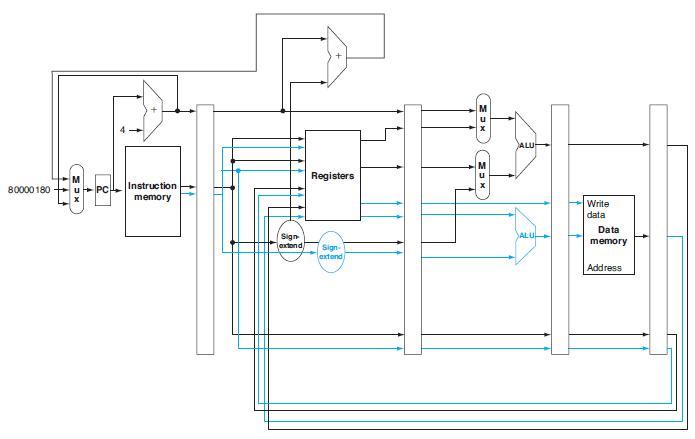

If the loop exits after executing only two iterations, draw a pipeline diagram for your MIPS code from 4.28.1 executed on a 2-issue processor

shown in Figure 4.69. Assume the processor has perfect branch prediction and can fetch any two instructions (not just consecutive instructions) in the same cycle.

Exercise 4.28.1

Translate this C code into MIPS instructions. Your translation should be direct, without rearranging instructions to achieve better performance.

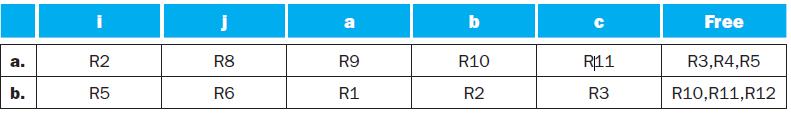

In this exercise we compare the performance of 1-issue and 2-issue processors, taking into account program transformations that can be made to optimize for 2-issue execution. Problems in this exercise refer to the following loop (written in C):![a. for(i=0;i!-j;i+=2) a[i+1]=a[i]; b. for(i=0; i-j;i+=2) b[i]-a[i]-a[i+1]; C Code](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1698/3/0/6/885653a1b454551c1698306883241.jpg)

When writing MIPS code, assume that variables are kept in registers as follows, and that all registers except those indicated as Free are used to keep various variables, so they cannot be used for anything else.

80000180 UPC Instruction memory ++ Sign- Taxtand Registers Sign- extend (EX ALU ALU Write data Data memory Address

Step by Step Solution

3.53 Rating (160 Votes )

There are 3 Steps involved in it

The MIPS code for each of the C code loops would lo... View full answer

Get step-by-step solutions from verified subject matter experts