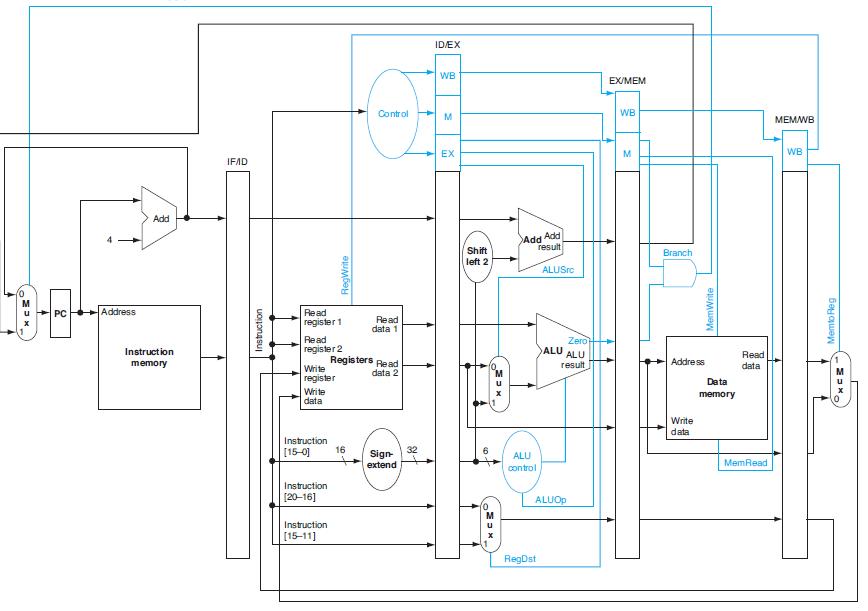

Question: What is the value of the PCSrc signal for this instruction? This signal is generated early in the MEM stage (only a single AND gate).

What is the value of the PCSrc signal for this instruction? This signal is generated early in the MEM stage (only a single AND gate). What would be a reason in favor of doing this in the EX stage? What is the reason against doing it in the EX stage?

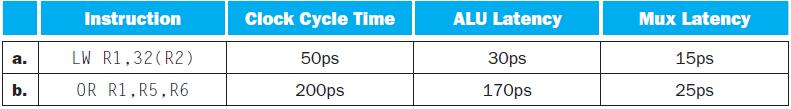

The first three problems in this exercise refer to the execution of the following instruction in the pipelined datapath from Figure 4.51, and assume the following clock cycle time, ALU latency, and Mux latency:

Figure 4.51

a. b. Instruction LW R1,32(R2) OR R1, R5, R6 Clock Cycle Time 50ps 200ps ALU Latency 30ps 170ps Mux Latency 15ps 25ps

Step by Step Solution

3.48 Rating (151 Votes )

There are 3 Steps involved in it

Value of PCSrc Signal The PCSrc signal determines whether the next value of the program counter PC s... View full answer

Get step-by-step solutions from verified subject matter experts