Question: Repeat 4.6.2, but this time we need to support only conditional PC-relative branches. Problem 4.6.2 Consider a datapath similar to the one in Figure 4.11,

Repeat 4.6.2, but this time we need to support only conditional PC-relative branches.

Problem 4.6.2

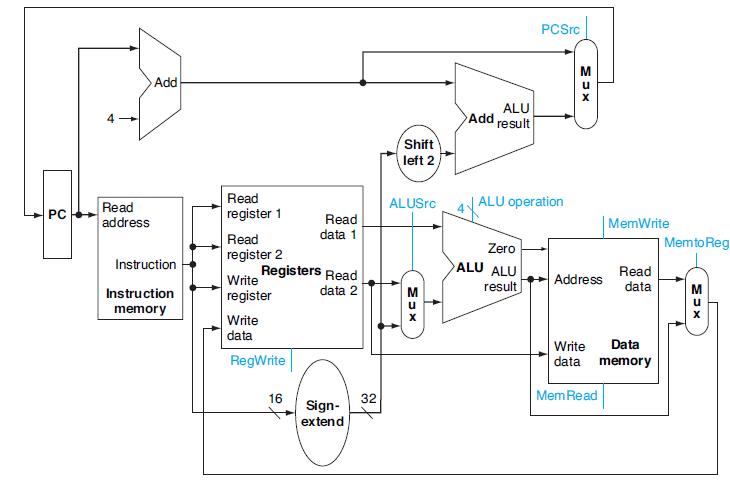

Consider a datapath similar to the one in Figure 4.11, but for a processor that only has one type of instruction: unconditional PC-relative branch. What would the cycle time be for this datapath?

Figure 4.11

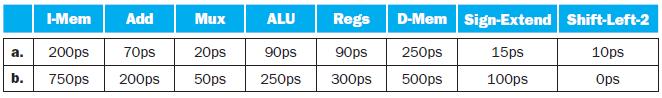

Problems in this exercise assume that logic blocks needed to implement a processor’s datapath have the following latencies:

PC Read address Add Instruction Instruction memory Read register 1 Read register 2 Write register Write data Registers Read data 2 RegWrite Read data 1 16 Sign- extend 32 Shift left 2 ALUSrc MUX >Add ALU result PCSrc ALU operation Zero ALU ALU result MUX Address MemWrite Mem Read Read data Write Data data memory Mem to Reg MUX

Step by Step Solution

3.42 Rating (142 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts