Question: Redesign the priority encoder from Exercise 2.36 to be as fast as possible. You may use any of the gates from Table 2.8. Sketch the

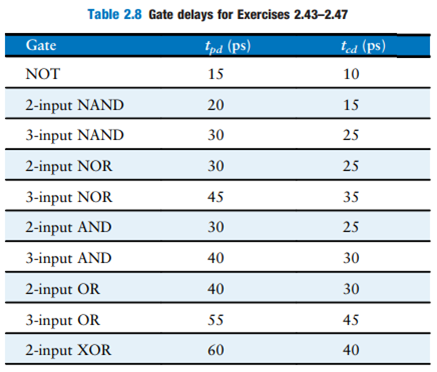

Redesign the priority encoder from Exercise 2.36 to be as fast as possible. You may use any of the gates from Table 2.8. Sketch the new circuit and indicate the critical path. What are its propagation delay and contamination delay?

Table 2.8 Gate delays for Exercises 2.432.47 (sd) Pd, 15 Gate ted (ps) NOT 10 15 2-input NAND 20 3-input NAND 30 25 2-input NOR 30 25 3-input NOR 45 35 2-input AND 30 25 3-input AND 40 30 2-input OR 40 30 3-input OR 55 45 2-input XOR 60 40

Step by Step Solution

3.40 Rating (159 Votes )

There are 3 Steps involved in it

To redesign the priority encoder for maximum speed we need to optimize the logic circuit to minimize both propagation delay t p d t p d and contaminat... View full answer

Get step-by-step solutions from verified subject matter experts