Question: A simple binary counter has only a clock input (Ck 1 ). The counter increments on the rising edge of Ck 1 . (a) Show

(a) Show the proper connections for a signal En and the system clock (CLK), so that when En = 1, the counter increments on the rising edge of CLK and when En = 0, the counter does not change state.

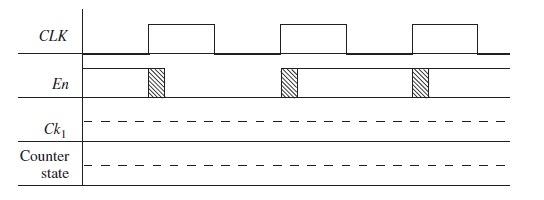

(b) Complete the following timing diagram. Explain in terms of your diagram why the switching transients that occur on En after the rising edge of CLK do not affect the proper operation of the counter.

CLK En Ck Counter state

Step by Step Solution

3.44 Rating (157 Votes )

There are 3 Steps involved in it

a b The clock input to the NAND gate in a is inverted ... View full answer

Get step-by-step solutions from verified subject matter experts