Question: (1) Design a 4-bit shift register with the following interface specification Signal Mode #bits Description clock input 1 clock signal reset input 1 synchronous reset;

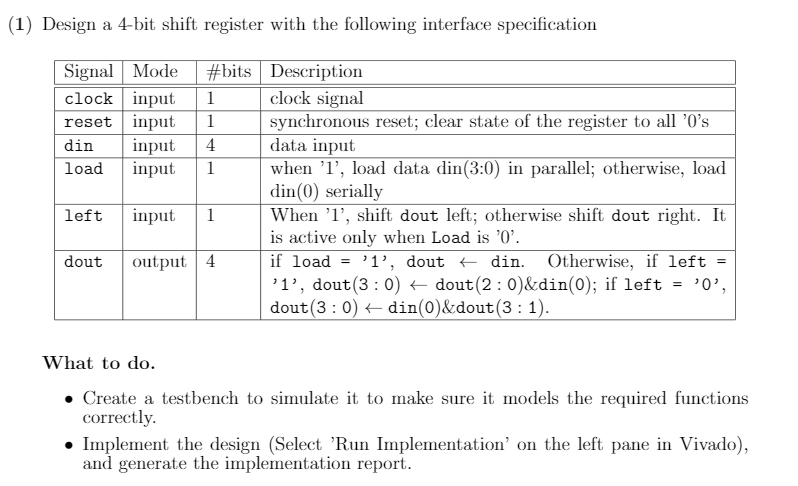

(1) Design a 4-bit shift register with the following interface specification Signal Mode #bits Description clock input 1 clock signal reset input 1 synchronous reset; clear state of the register to all O's din input 4 data input load input 1 when 'l', load data din(3:0) in parallel; otherwise, load din(0) serially left input 1 When '1', shift dout left; otherwise shift dout right. It is active only when Load is 'O'. dout output 4 if load '1', dout + din. Otherwise, if left = '1', dout(3:0) + dout(2:0)&din(0); if left '0', dout(3:0) + din(0)&dout(3:1). What to do. Create a testbench to simulate it to make sure it models the required functions correctly. Implement the design (Select 'Run Implementation on the left pane in Vivado), and generate the implementation report

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts