Question: 1 . This exercise is intended to help you understand the relationship between delay slots, control hazards, and branch execution in a pipelined processor. In

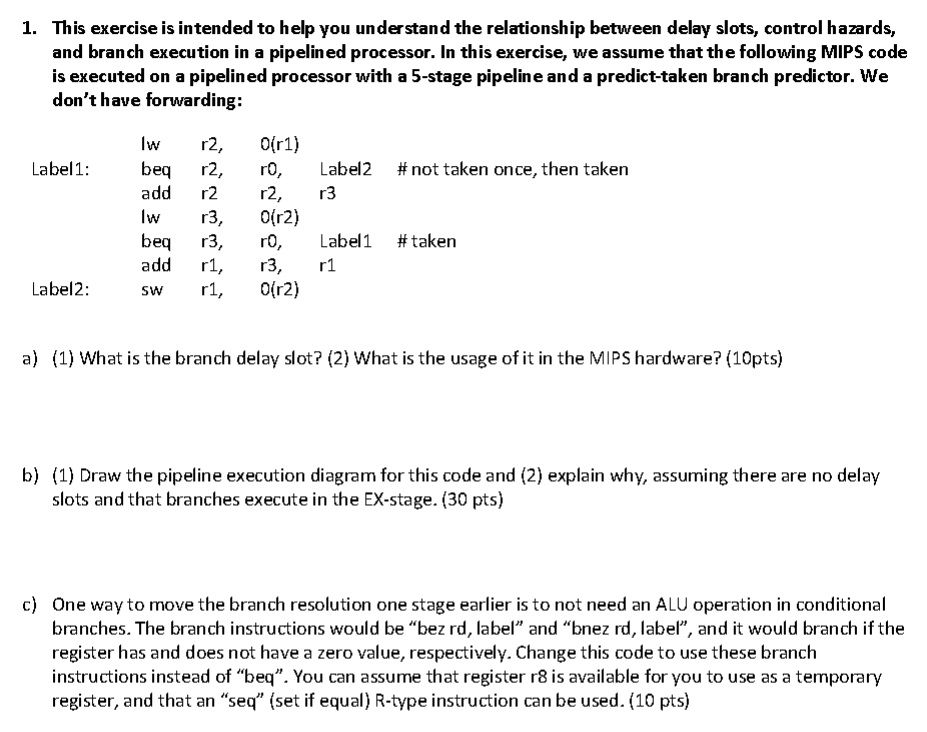

This exercise is intended to help you understand the relationship between delay slots, control hazards, and branch execution in a pipelined processor. In this exercise, we assume that the following MIPS code is executed on a pipelined processor with a stage pipeline and a predicttaken branch predictor. We don't have forwarding:

a What is the branch delay slot? What is the usage of it in the MIPS hardware? pts

b Draw the pipeline execution diagram for this code and explain why, assuming there are no delay slots and that branches execute in the EXstage. pts

c One way to move the branch resolution one stage earlier is to not need an ALU operation in conditional branches. The branch instructions would be "bez rd label" and "bnez rd label", and it would branch if the register has and does not have a zero value, respectively. Change this code to use these branch instructions instead of "beq". You can assume that register r is available for you to use as a temporary register, and that an "seq" set if equal Rtype instruction can be used. pts

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock