Question: This exercise is intended to help you understand the relationship between delay slots, control hazards, and branch execution in a pipelined processor. In this exer-

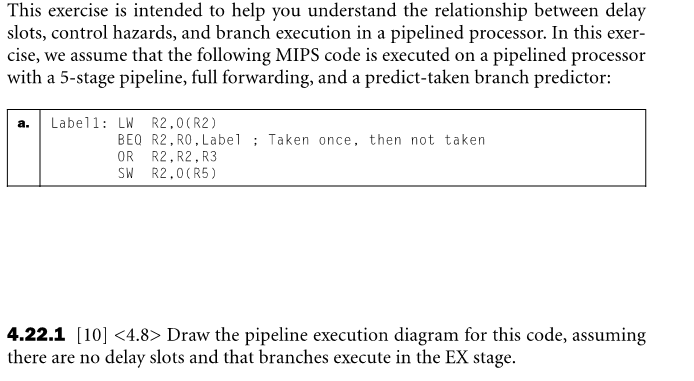

This exercise is intended to help you understand the relationship between delay slots, control hazards, and branch execution in a pipelined processor. In this exer- cise, we assume that the following MIPS code is executed on a pipelined processor with a 5-stage pipeline, full forwarding, and a predict-taken branch predictor: a. Label1: LW R2.0(R2) BEO R2, RO,LabelTaken once, then not taken OR R2,R2,R3 SW R2,0(R5) 4.22.1 [10] Draw the pipeline execution diagram for this code, assuming there are no delay slots and that branches execute in the EX stage

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts