Question: 2. Consider executing the following assembly code in MIPS five stage (IF, ID, EX, ME, WB) pipeline model: a. Assume there is only one memory

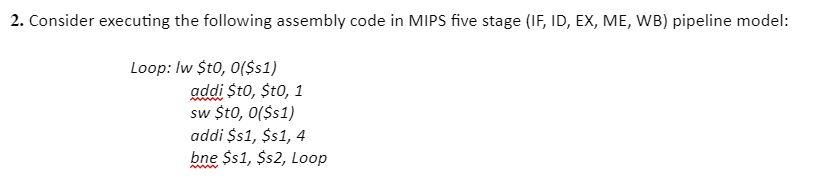

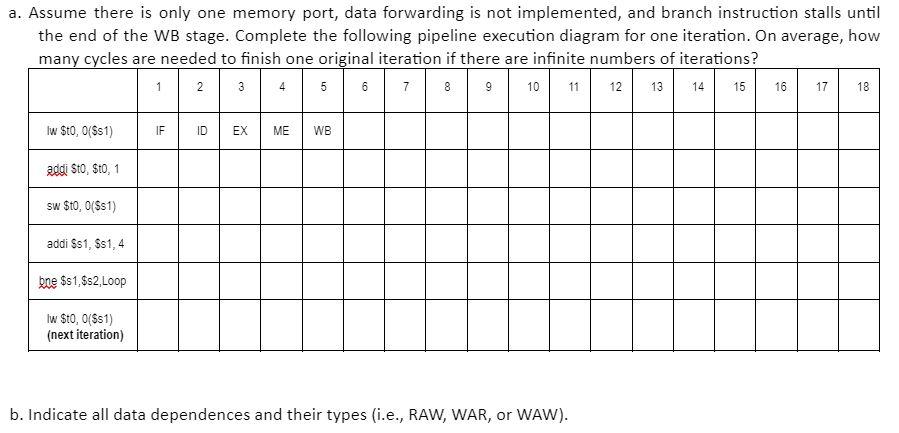

2. Consider executing the following assembly code in MIPS five stage (IF, ID, EX, ME, WB) pipeline model: a. Assume there is only one memory port, data forwarding is not implemented, and branch instruction stalls until the end of the WB stage. Complete the following pipeline execution diagram for one iteration. On average, how many cycles are needed to finish one original iteration if there are infinite numbers of iterations? b. Indicate all data dependences and their types (i.e., RAW, WAR, or WAW)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts