Question: 2) In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this sssum that ihe datsath have he

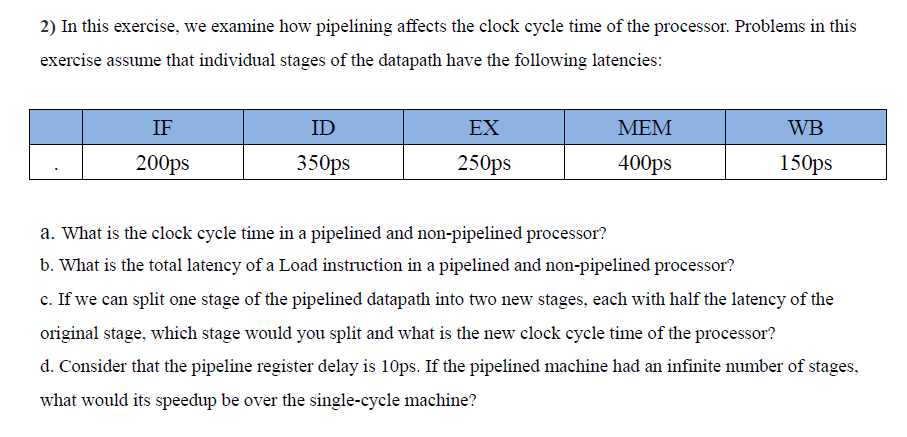

2) In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this sssum that ihe datsath have he folowing latenscies IF ID EX MEM WB 200ps 350ps 250ps400ps 150ps a. What is the clock cycle time in a pipelined and non-pipelined processor? b. What is the total latency of a Load instruction in a pipelined and non-pipelined processor? c. If we can split one stage of the pipelined datapath into two new stages, each with half the latency of the original stage, which stage would you split and what is the new clock cycle time of the processor? d. Consider that the pipeline register delay is 10ps. If the pipelined machine had an infinite number of stages, what would its speedup be over the single-cycle machine

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts