Question: 3. Consider a CMOS inverter whose input is at 2.5V and output at 0V. The nMOS device is 1 um wide and the pMOS device

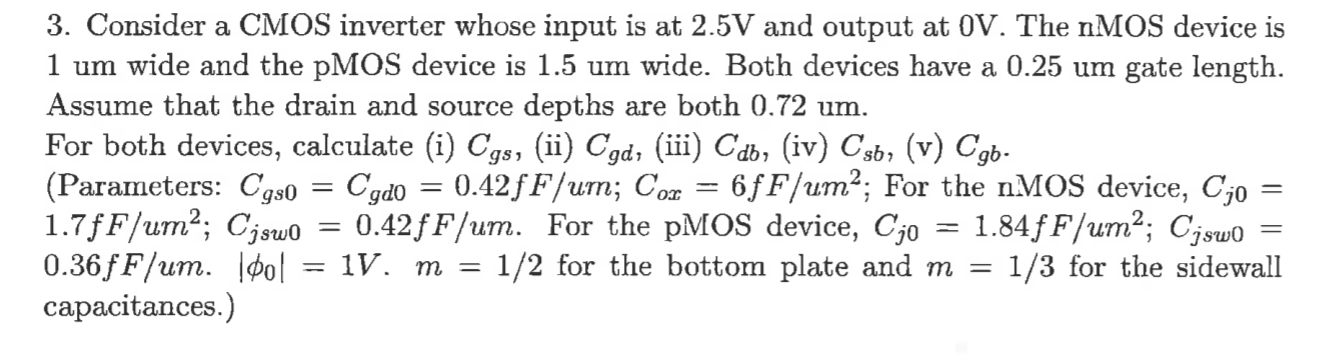

3. Consider a CMOS inverter whose input is at 2.5V and output at 0V. The nMOS device is 1 um wide and the pMOS device is 1.5 um wide. Both devices have a 0.25 um gate length. Assume that the drain and source depths are both 0.72 um. For both devices, calculate (i) Cgs, (ii) Cgd, (iii) Cdb, (iv) Csb, (v) Cgb. (Parameters. Cgs,-Cgdo 0.42fF/um. Cor-6fF/um2. For the nMOS device, Go = 1.7fF/un2 Cjsuo 0.42fF/um. For the pMOS device, Cjo 1.84fF/um2 Cj 0.36fF/um. ldol = 1V. m = 1/2 for the bottom plate and m-1/3 for the sidewall capacitances.) 3. Consider a CMOS inverter whose input is at 2.5V and output at 0V. The nMOS device is 1 um wide and the pMOS device is 1.5 um wide. Both devices have a 0.25 um gate length. Assume that the drain and source depths are both 0.72 um. For both devices, calculate (i) Cgs, (ii) Cgd, (iii) Cdb, (iv) Csb, (v) Cgb. (Parameters. Cgs,-Cgdo 0.42fF/um. Cor-6fF/um2. For the nMOS device, Go = 1.7fF/un2 Cjsuo 0.42fF/um. For the pMOS device, Cjo 1.84fF/um2 Cj 0.36fF/um. ldol = 1V. m = 1/2 for the bottom plate and m-1/3 for the sidewall capacitances.)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts