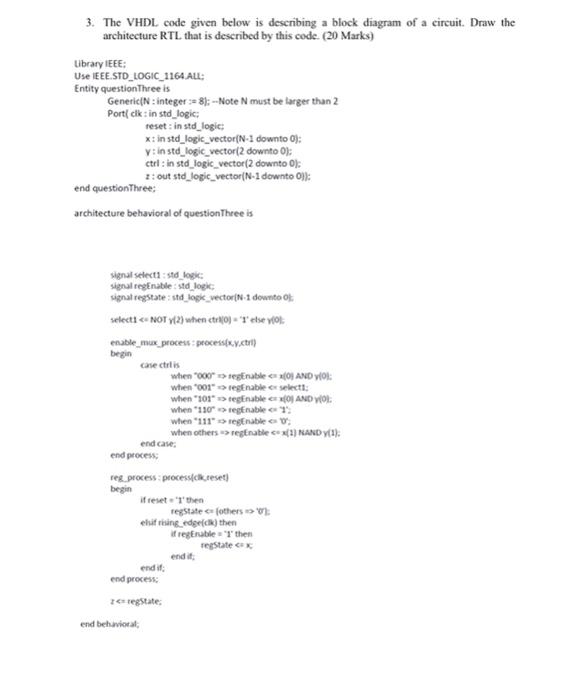

Question: 3. The VHDL code given below is describing a block diagram of a circuit. Draw the architecture RTL that is described by this code (20

3. The VHDL code given below is describing a block diagram of a circuit. Draw the architecture RTL that is described by this code (20 Marks) Library IEEE: Use IEEE.STD_LOGIC_1164 ALL: Entity questionThree is GenericN: integer = 8): --Note N must be larger than 2 Port cl:in std_logic reset: in std_logic X:in std_logic_vector(N-1 downto 0); Y: instd_logic_vector(2 downto 0); ctrl : in std_logic_vector(2 downto 0); z: out std_logic_vector(N-1 downto 0)); end questionThree: architecture behavioral of question Three is signal select:std_topic signal regEnable : std log: signat regstate std_logk_vector[N-1 downto Of selectie NOT Yi) when toetse von enable_mux process process.Y.ctt) begin carse ctrlis when 00segenable (0) AND OL: when"001">RegEnable select: when "101">tegEnable AND VIOL. when "110>regnable 1 when '111">RegEnable when others regnablece (2) RAND (1) end case, end process reg process processick reset) begin freset the regState others elif rising edge(ck) then regruble then restate cx end end process Iregstate end behavioral 3. The VHDL code given below is describing a block diagram of a circuit. Draw the architecture RTL that is described by this code (20 Marks) Library IEEE: Use IEEE.STD_LOGIC_1164 ALL: Entity questionThree is GenericN: integer = 8): --Note N must be larger than 2 Port cl:in std_logic reset: in std_logic X:in std_logic_vector(N-1 downto 0); Y: instd_logic_vector(2 downto 0); ctrl : in std_logic_vector(2 downto 0); z: out std_logic_vector(N-1 downto 0)); end questionThree: architecture behavioral of question Three is signal select:std_topic signal regEnable : std log: signat regstate std_logk_vector[N-1 downto Of selectie NOT Yi) when toetse von enable_mux process process.Y.ctt) begin carse ctrlis when 00segenable (0) AND OL: when"001">RegEnable select: when "101">tegEnable AND VIOL. when "110>regnable 1 when '111">RegEnable when others regnablece (2) RAND (1) end case, end process reg process processick reset) begin freset the regState others elif rising edge(ck) then regruble then restate cx end end process Iregstate end behavioral

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts