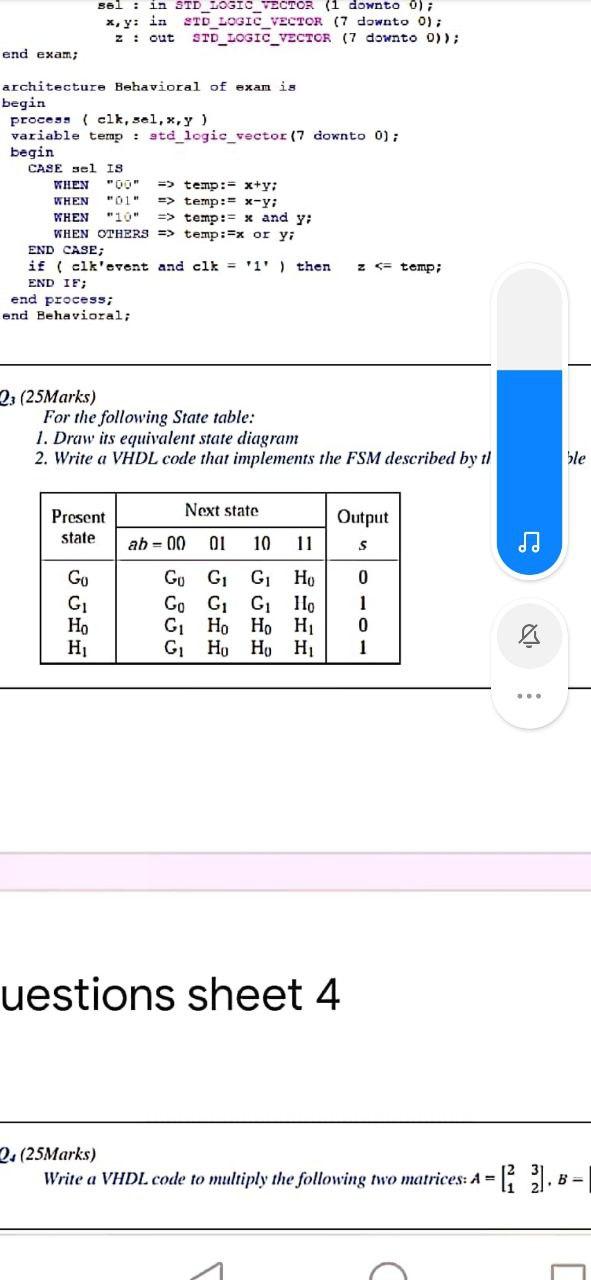

Question: 361 : in STD_LOGIC_VECTOR (1 downto 0); x,y: in CTD_LOGIC_VECTOR (7 downto 0); z : out STD_LOGIC_VECTOR (7 downto 0)); end exam; 0 architecture Behavioral

361 : in STD_LOGIC_VECTOR (1 downto 0); x,y: in CTD_LOGIC_VECTOR (7 downto 0); z : out STD_LOGIC_VECTOR (7 downto 0)); end exam; "0" architecture Behavioral of exam is begin process ( elk, sel,x,y) variable terap: atd_logic_vector (7 downto 0); begin CASE sel IS WHEN => temp:= x+y: WHEN "01" => temp:= x-yi WHEN => temp:= x and y: WHEN OTHERS => temp:=x or yi END CASE; if ( elk'event and clk = '1' ) then z (= temp; END IF; end process; end Behavioral; 23 (25Marks) For the following State table: 1. Draw its equivalent state diagram 2. Write a VHDL code that implements the FSM described by tl ble Next state Present state Output ab-00 01 10 11 S Go G1 HO , Go G G H Go GG Ho G Ha Ho H. G HU HU H 0 1 0 1 uestions sheet 4 2. (25Marks) Write a VHDL code to multiply the following two matrices: A = 21.B

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts