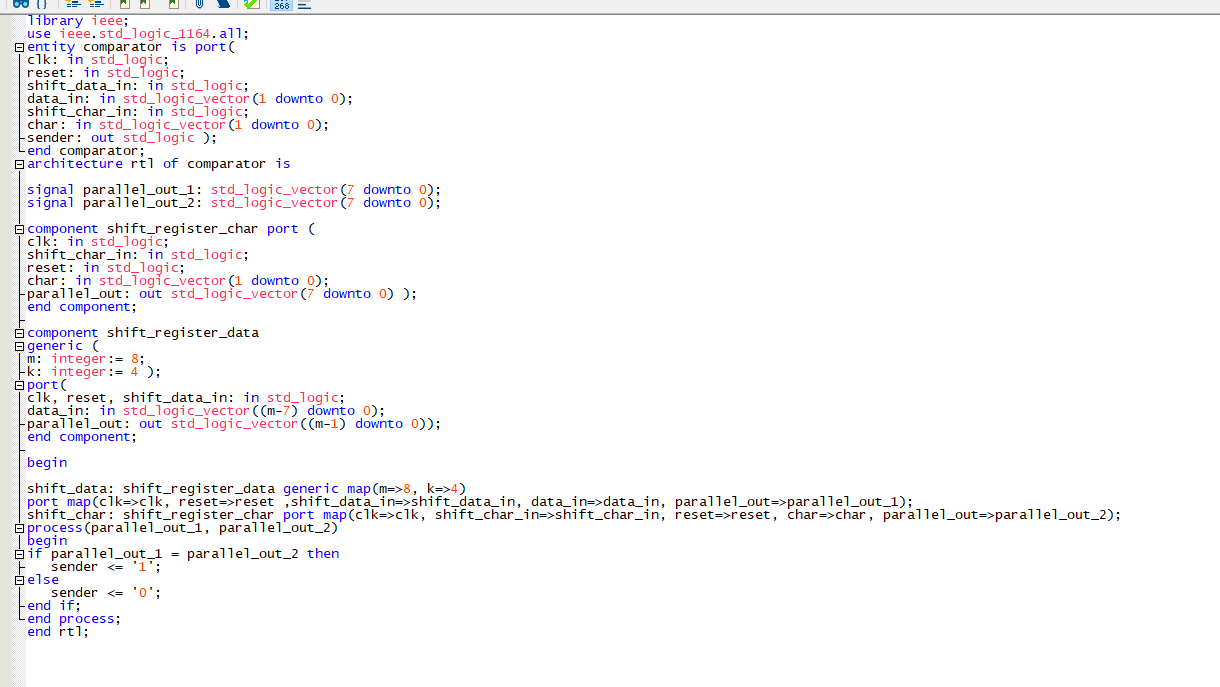

Question: I I need a testbench for the following code in VHDL intel quartus prime. Tibrary ieee; use ieee. std_7ogic_1164. a717; gentity comparator is port (

I

I need a testbench for the following code in VHDL intel quartus prime.

Tibrary ieee; use ieee. std_7ogic_1164. a717; gentity comparator is port ( c7k: in std_logic; reset: in std_logic; shift_data_in: in std_logic; data_in: in std_logic_vector (1 downto 0); shift_char_in: in std_logic; char:- in std_logic_vector ( 1 downto 0); -sender: out std_logic ); end comparator; architecture rt 1 of comparator is component shift_register_char port ( c7k: in std_logic; shift_char_in: in std_logic; reset: in std_logic; char: in std_7ogic_vector ( 1 downto 0 ); - paraile 1_out: out std_logic_vector (7 downto 0) ); end component; Gomponent shift_register_data goneric m : integer :=8; -k: integer: :=4) aportc c 7k, reset, shift_data_in: in std_logic; data_in: in std_logic_vector ((m7) downto 0); -para1ei_out: out std_logic_vector ((m1) downto 0)); end component; begin shift_data: shift_register_data generic map (m=>8,k>) port map(cik=>c7k, reset reset , shift_data_in=shift_data_in, data_in=>data_in, paral1el_out > paral1el_out_1); shift_char: shift_register_char_port map(c7k=>c7k, shift_char_in=>shift_char_in, resett=>eset, char =>char, para17e1_out=>para11el_out_2); Gprocess (para11e1_out_1, para11e1_out_2) begin if paralle1_out_1 = para11e1_out_2 then Getse sender

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts