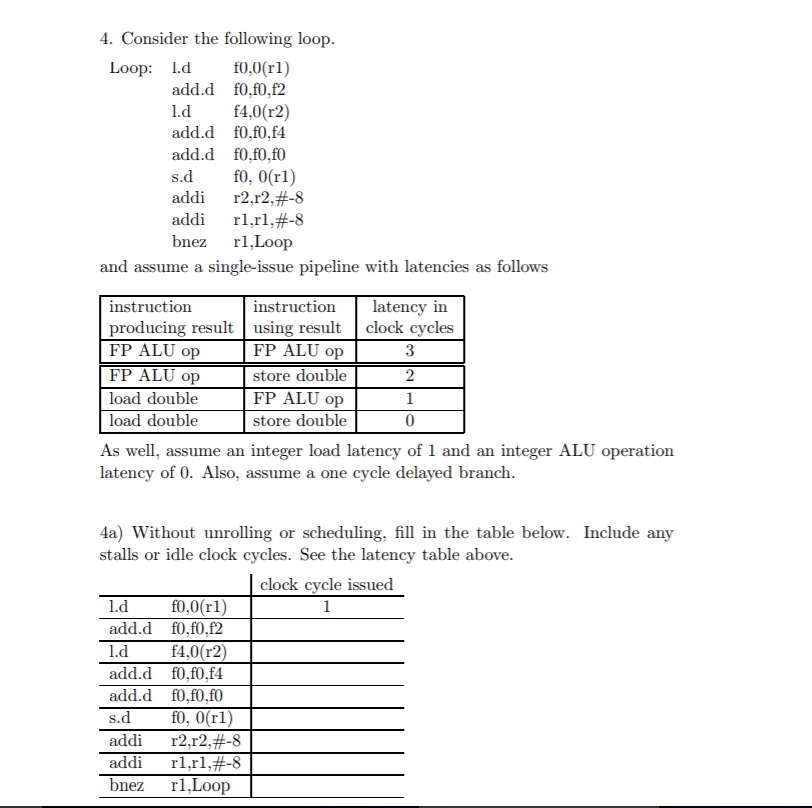

Question: 4. Consider the following loop Loop: d 0,0(rl) add.d f0,fo,f2 l.d f4,0(r2) add.d fo,f0.f4 add.d f0.f0.??? s.d f0, 0(r1) addi r2,r2,#-8 addi r1,r1,#-8 bnez r1,Loop

4. Consider the following loop Loop: d 0,0(rl) add.d f0,fo,f2 l.d f4,0(r2) add.d fo,f0.f4 add.d f0.f0.??? s.d f0, 0(r1) addi r2,r2,#-8 addi r1,r1,#-8 bnez r1,Loop and assume a single-issue pipeline with latencies as follows instruction producing result using FP ALU op FP ALU op load double load double instructionlaten result clock cycles FP ALU op store double FP ALU op store double As well, assume an integer load latency of 1 and an integer ALU operation latency of 0. Also, assume a one cycle delayed branch 4a) Without unrolling or scheduling, fill in the table below. Include any stalls or idle clock cycles. See the latency table above clock cycle issued l.d f0,0(r1) add.d fo.fo.f2 1.d add.d ?.fo.f4 add.d fo,f0,f0 addi addi bnez f0, 0(rl) r2.r2.#-8 r1.r1.#-8 rl.Loop

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts