Question: 4. Given a 4KiB direct-mapped cache with block size of 16 bytes (assume write-back write allocate policy). The memory is byte-addressed. Trace through the following

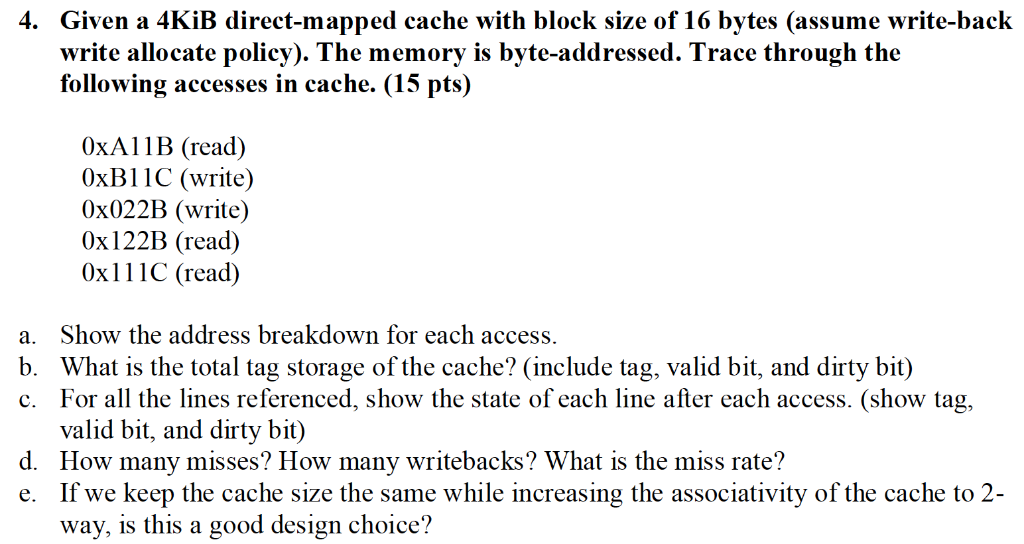

4. Given a 4KiB direct-mapped cache with block size of 16 bytes (assume write-back write allocate policy). The memory is byte-addressed. Trace through the following accesses in cache. (15 pts) 0xAllB (read) OxBl 1C (write) 0x022B (write) 0x122B (read) 0xl11C (read) a. Show the address breakdown for each access, b. What is the total tag storage of the cache? (include tag, valid bit, and dirty bit) c. For all the lines referenced, show the state of each line after each access. (show tag, valid bit, and dirty bit) d.How many misses? How many writebacks? What is the miss rate? e. If we keep the cache size the same while increasing the associativity of the cache to 2- way, is this a good design choice

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts