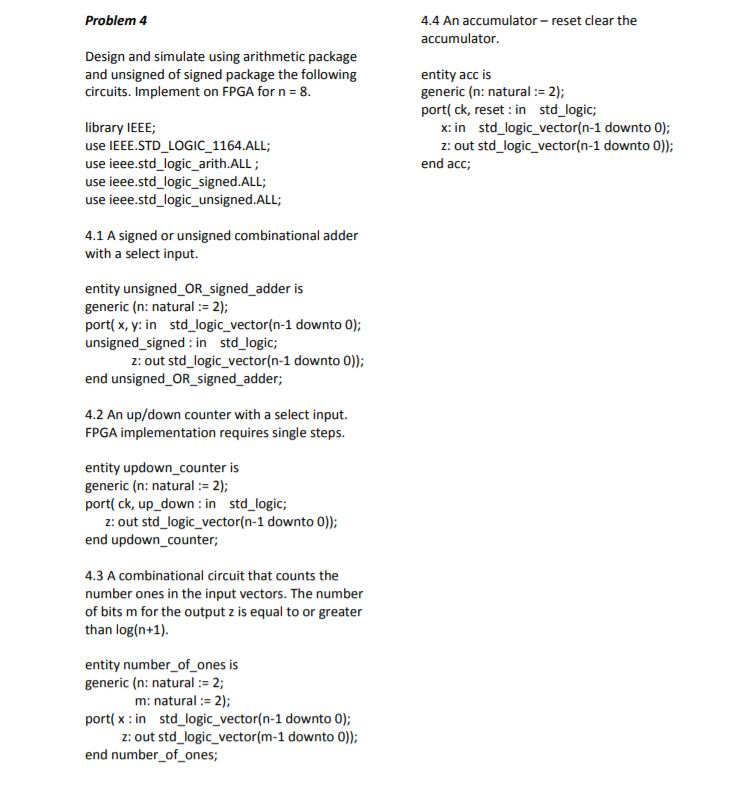

Question: 4.4 An accumulator- reset clear the accumulator Problem 4 Design and simulate using arithmetic package and unsigned of signed package the following circuits. Implement on

4.4 An accumulator- reset clear the accumulator Problem 4 Design and simulate using arithmetic package and unsigned of signed package the following circuits. Implement on FPGA for n 8 entity acc is generic (n: natural-2); port( ck, reset: in std logic; x: in std_logic_vector(n-1 downto 0); z: out std_logic vector(n-1 downto 0)); library IEEE; use IEEE.STD LOGIC 1164.ALL; use ieee.std logic arith.ALL; use ieee.std_logic signed.ALL; use ieee.std_logic unsigned.ALL; end acc; 4.1 A signed or unsigned combinational adder with a select input. entity unsigned_OR signed_adder is generic (n: natural-2); port(x, y: in std logic_vector(n-1 downto 0); unsigned_signed: in std logic; z: out std logic vector(n-1 downto O)): end unsigned_OR_signed adder; 4.2 An up/down counter with a select input. FPGA implementation requires single steps. entity updown_counter is generic (n: natural2): port( ck, up_down: in std_logic; z: out stdlogic vector(n-1 downto O)); end updown_counter; 4.3 A combinational circuit that counts the number ones in the input vectors. The number of bits m for the output z is equal to or greater than log(n+1). entity number of ones is generic (n: natural 2; m: natural-2); port(x: n std_logic_vector(n-1 downto 0); z: out std logic vector(m-1 downto O)) end number of ones; 4.4 An accumulator- reset clear the accumulator Problem 4 Design and simulate using arithmetic package and unsigned of signed package the following circuits. Implement on FPGA for n 8 entity acc is generic (n: natural-2); port( ck, reset: in std logic; x: in std_logic_vector(n-1 downto 0); z: out std_logic vector(n-1 downto 0)); library IEEE; use IEEE.STD LOGIC 1164.ALL; use ieee.std logic arith.ALL; use ieee.std_logic signed.ALL; use ieee.std_logic unsigned.ALL; end acc; 4.1 A signed or unsigned combinational adder with a select input. entity unsigned_OR signed_adder is generic (n: natural-2); port(x, y: in std logic_vector(n-1 downto 0); unsigned_signed: in std logic; z: out std logic vector(n-1 downto O)): end unsigned_OR_signed adder; 4.2 An up/down counter with a select input. FPGA implementation requires single steps. entity updown_counter is generic (n: natural2): port( ck, up_down: in std_logic; z: out stdlogic vector(n-1 downto O)); end updown_counter; 4.3 A combinational circuit that counts the number ones in the input vectors. The number of bits m for the output z is equal to or greater than log(n+1). entity number of ones is generic (n: natural 2; m: natural-2); port(x: n std_logic_vector(n-1 downto 0); z: out std logic vector(m-1 downto O)) end number of ones

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts