Question: 6. (6pt) In this exercise, we examine how pipelining affects the clock cycle time of the processor. Assume that individual stages of the data path

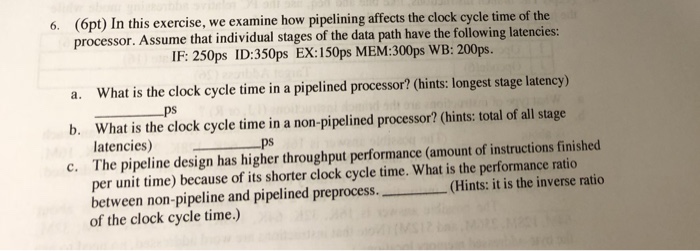

6. (6pt) In this exercise, we examine how pipelining affects the clock cycle time of the processor. Assume that individual stages of the data path have the following latencies: a. What is the clock cycle time in a pipelined processor? (hints: longest stage latency) b. What is the clock cycle time in a non-pipelined processor? (hints: total of all stage IF: 250ps ID:350ps EX:150ps MEM.300ps WB: 200ps. ps latencies) The pipeline design has higher throughput performance (amount of instructions finished per unit time) because of its shorter clock cycle time. What is the performance ratio between non-pipeline and pipelined preprocess.(Hints: it is the inverse ratio of the clock cycle time.) .ps c

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts