Question: 8) Using the code below draw the circuit. Label all wires with the given signal name. (3 points) library ieee; use ieee.std_logic_1164.all; entity variables is

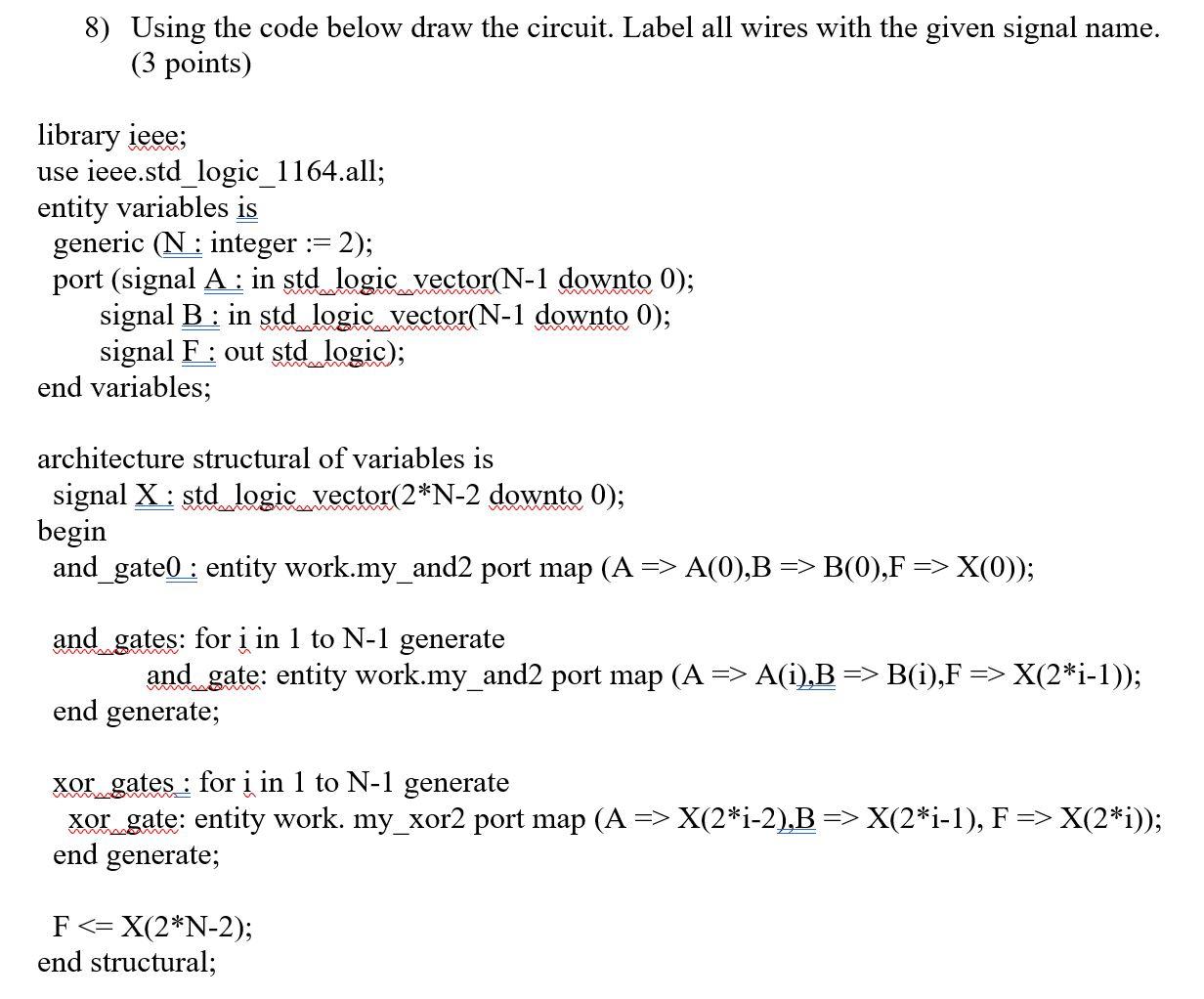

8) Using the code below draw the circuit. Label all wires with the given signal name. (3 points) library ieee; use ieee.std_logic_1164.all; entity variables is generic (N: integer := 2); port (signal A : in std logic vector(N-1 downto 0); signal B : in std logic vector(N-1 downto 0); signal F: out std logic); end variables; architecture structural of variables is signal X : std. logic vector(2*N-2 downto 0); begin and_gate0 : entity work.my_and2 port map (A => A(0),B => B(0),F => X(0)); and gates: for i in 1 to N-1 generate and gate: entity work.my_and2 port map (A => A(i),B => B(i),F => X(2*i-1)); end generate; xor, gates : for i in 1 to N-1 generate xor gate: entity work. my_xor2 port map (A => X(2*i-2),B => X(2*i-1), F => X(2*i)); end generate; F A(0),B => B(0),F => X(0)); and gates: for i in 1 to N-1 generate and gate: entity work.my_and2 port map (A => A(i),B => B(i),F => X(2*i-1)); end generate; xor, gates : for i in 1 to N-1 generate xor gate: entity work. my_xor2 port map (A => X(2*i-2),B => X(2*i-1), F => X(2*i)); end generate; F

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts