Question: (a) If this MIPS CPU has no forwarding capability, indicate all possible hazards. (b) Assuming this MIPS CPU has full forwarding capability to solve any

(a) If this MIPS CPU has no forwarding capability, indicate all possible hazards. (b) Assuming this MIPS CPU has full forwarding capability to solve any hazards that can be solved, what is the speed-up achieved by adding full forwarding to the original CPU that had no forwarding?

(a) If this MIPS CPU has no forwarding capability, indicate all possible hazards. (b) Assuming this MIPS CPU has full forwarding capability to solve any hazards that can be solved, what is the speed-up achieved by adding full forwarding to the original CPU that had no forwarding?

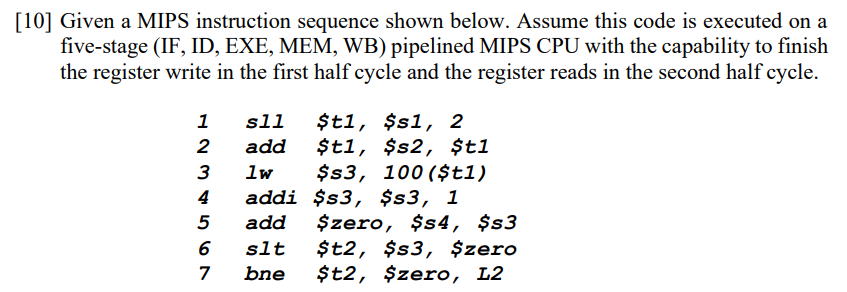

[10] Given a MIPS instruction sequence shown below. Assume this code is executed on a five-stage (IF, ID, EXE, MEM, WB) pipelined MIPS CPU with the capability to finish the register write in the first half cycle and the register reads in the second half cycle. 1234567s11add1waddiaddsltbne$t1,$s1,2$t1,$s2,$t1$s3,100($t1)$s3,$s3,1$zero,$s4,$s3$t2,$s3,$zero$t2,$zero,L2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts