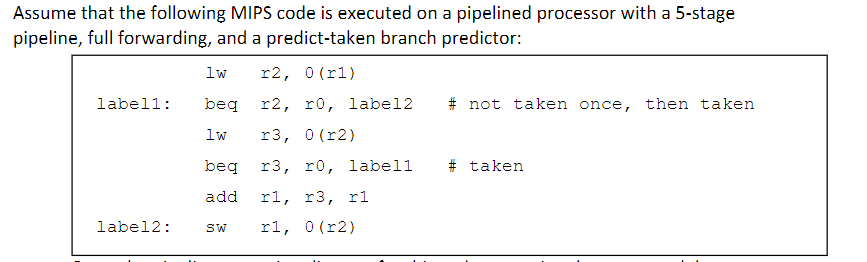

Question: Assume that the following MIPS code is executed on a pipelined processor with a 5-stage pipeline, full forwarding, and a predict-taken branch predictor lw r2,

Assume that the following MIPS code is executed on a pipelined processor with a 5-stage pipeline, full forwarding, and a predict-taken branch predictor lw r2, 0 (r1) label 1 : ro, 21abe 12 beq r2, not taken once, then taken 1w r3, 0 (r2) beq r3, r0, 1abe 11 # taken add r1, r3, rl label2: Sw rl, 0 (r2) Assume that the following MIPS code is executed on a pipelined processor with a 5-stage pipeline, full forwarding, and a predict-taken branch predictor lw r2, 0 (r1) label 1 : ro, 21abe 12 beq r2, not taken once, then taken 1w r3, 0 (r2) beq r3, r0, 1abe 11 # taken add r1, r3, rl label2: Sw rl, 0 (r2)

Step by Step Solution

There are 3 Steps involved in it

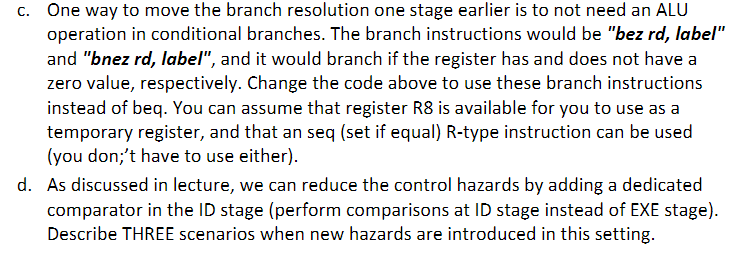

Solution Part c To change the code using bez and bnez instructions here is the modified code plainte... View full answer

Get step-by-step solutions from verified subject matter experts