Question: Draw the pipeline execution diagram for this code, assuming there are no delay slots and that branches execute in the EX stage. This exercise is

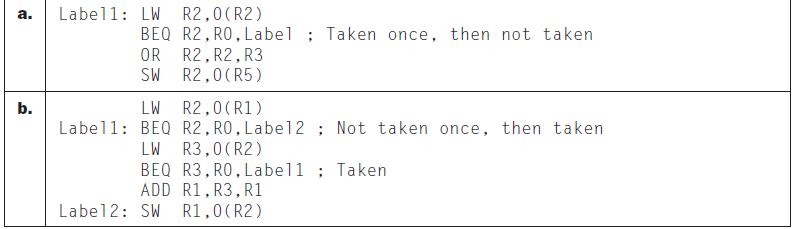

Draw the pipeline execution diagram for this code, assuming there are no delay slots and that branches execute in the EX stage.

This exercise is intended to help you understand the relationship between delay slots, control hazards, and branch execution in a pipelined processor. In this exercise, we assume that the following MIPS code is executed on a pipelined processor with a 5-stage pipeline, full forwarding, and a predict-taken branch predictor:

a. b. Label1: LW R2,0 (R2) BEQ OR SW R2, RO, Label; Taken once, then not taken R2, R2, R3 R2,0 (R5) LW R2,0 (R1) Label1: BEQ R2, RO, Labe12; Not taken once, then taken LW R3,0 (R2) BEQ ADD Label2: SW R3, RO, Labell; Taken R1, R3, R1 R1,0 (R2)

Step by Step Solution

3.49 Rating (156 Votes )

There are 3 Steps involved in it

I am unable to physically draw diagrams but I can explain how you can create the pipeline execution diagrams for the given MIPS code which will help y... View full answer

Get step-by-step solutions from verified subject matter experts