Question: Assume the two-issue, statically scheduled processor for this exercise has the following properties: 1. One instruction must be a memory operation; the other must be

Assume the two-issue, statically scheduled processor for this exercise has the following properties: 1. One instruction must be a memory operation; the other must be an arithmetic/logic instruction or a branch. 2. The processor has all possible forwarding paths between stages (including paths to the ID stage for branch resolution). 3. The processor has perfect branch prediction. 4. Two instruction may not issue together in a packet if one depends on the other. (See page 324.) 5. If a stall is necessary, both instructions in the issue packet must stall. (See page 324.) As you complete these exercises, notice how much effort goes into generating code that will produce a near-optimal speedup.

question:

4.31.2 [10] What is the speedup of going from a one-issue to a two-issue processor? (Assume the loop runs thousands of iterations.)

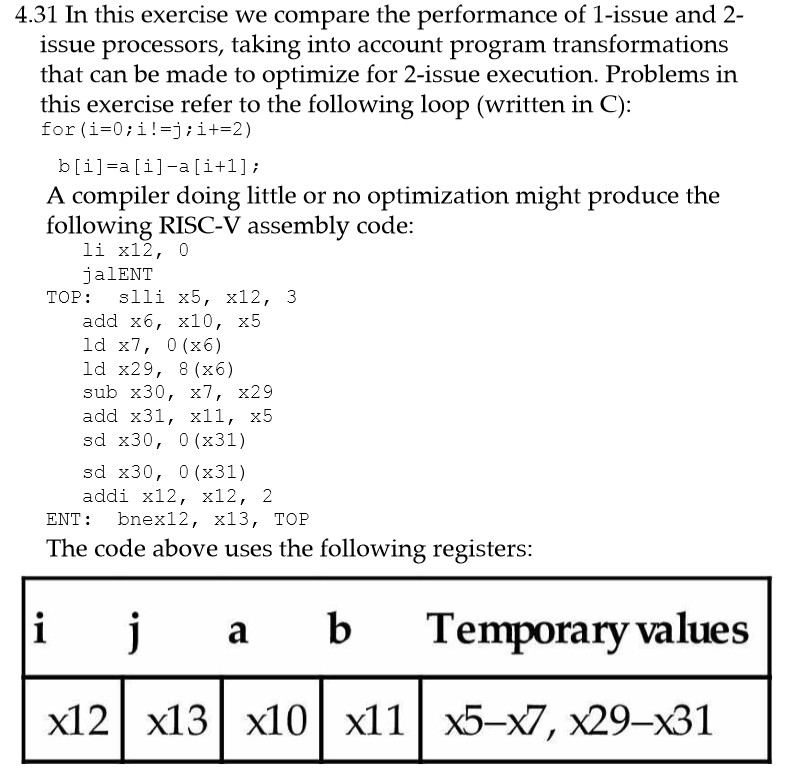

4.31 In this exercise we compare the performance of 1-issue and 2- issue processors, taking into account program transformations that can be made to optimize for 2-issue execution. Problems in this exercise refer to the following loop (written in C) A compiler doing little or no optimization might produce the following RISC-V assembly code: li x12, 0 jalENT TOP slli x5, x12, 3 add x6, x10, x5 ld x7, 0 (x6) ld x29, 8 (x6) sub x30, x7, x29 add x31, xll, x5 sd x30, 0 (x31) sd x30, 0 (x31) addi x12, x12, 2 ENT bnexl2, x13, TOP The code above uses the following registers: Temporary value x12 x13 x10 x11 x5-X7, X29-31 4.31 In this exercise we compare the performance of 1-issue and 2- issue processors, taking into account program transformations that can be made to optimize for 2-issue execution. Problems in this exercise refer to the following loop (written in C) A compiler doing little or no optimization might produce the following RISC-V assembly code: li x12, 0 jalENT TOP slli x5, x12, 3 add x6, x10, x5 ld x7, 0 (x6) ld x29, 8 (x6) sub x30, x7, x29 add x31, xll, x5 sd x30, 0 (x31) sd x30, 0 (x31) addi x12, x12, 2 ENT bnexl2, x13, TOP The code above uses the following registers: Temporary value x12 x13 x10 x11 x5-X7, X29-31

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts