Question: Problem # 1 Assume the following RISC - V assembly code: ` ` ` addi x 1 2 , x 1 2 , 0

Problem #

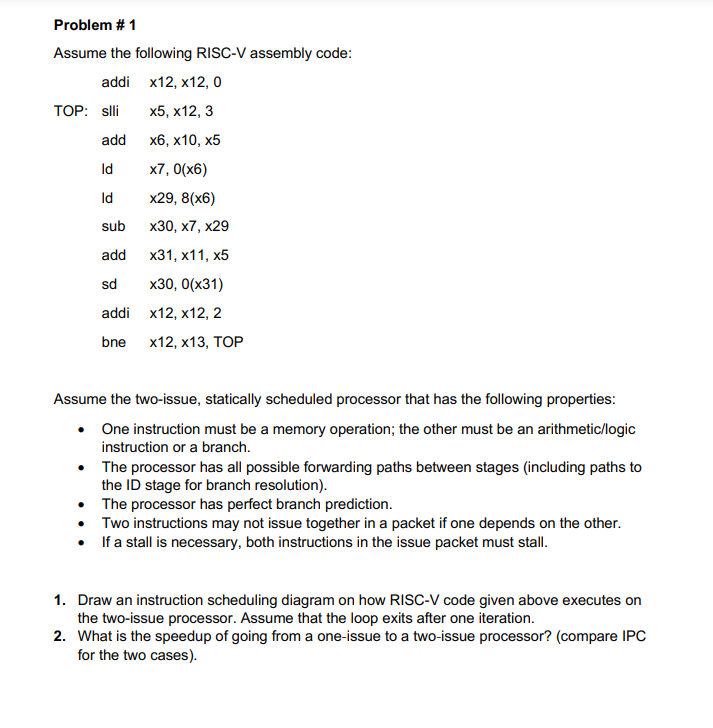

Assume the following RISCV assembly code:

addi x x

TOP: slli x x

add x x x

ld xx

ld xx

sub x x x

add x x x

sd xx

addi x x

bne x x TOP

Assume the twoissue, statically scheduled processor that has the following properties:

One instruction must be a memory operation; the other must be an arithmeticlogic instruction or a branch.

The processor has all possible forwarding paths between stages including paths to the ID stage for branch resolution

The processor has perfect branch prediction.

Two instructions may not issue together in a packet if one depends on the other.

If a stall is necessary, both instructions in the issue packet must stall.

Draw an instruction scheduling diagram on how RISCV code given above executes on the twoissue processor. Assume that the loop exits after one iteration.

What is the speedup of going from a oneissue to a twoissue processor? compare IPC for the two cases

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock