Question: Build a synchronous counter called cntr. The module will be parameterizable by its width and the corresponding initialization vector. Counter interface, in addition to the

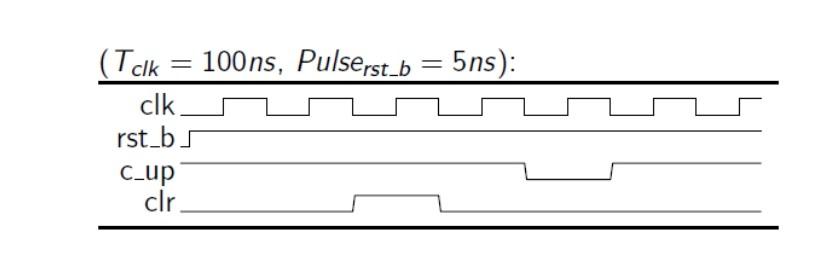

Build a synchronous counter called cntr. The module will be parameterizable by its width and the corresponding initialization vector. Counter interface, in addition to the clk signal, it will include the following signals: rst_b, asynchronous, active on 0, will set the contents of the register to the vector of initialization. c_up, synchronous, active on 1, increments the counter value. clr, synchronous, active on 1, will set the content to the initialization vector, with higher priority than c_up signal. q, the output, represents the contents of the counter. Parameterize the 8-bit counter with an initialization vector having 8'hff value and test the module with the entries generated from the May schedule down:

(T clk = 100ns, Pulserst_b = 5ns): clk rst_b_s C_up clr

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts