Question: Can someone help me with the verilog code for this? 2's complement multiplier, design. Design a multiplier for 2's complement binary numbers. Consider two approaches:

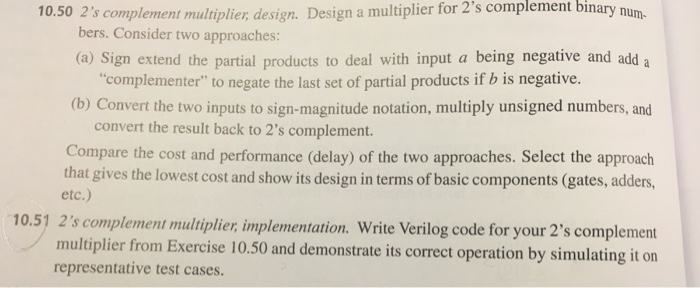

2's complement multiplier, design. Design a multiplier for 2's complement binary numbers. Consider two approaches: Sign extend the partial products to deal with input a being negative and add a "complementer" to negate the last set of partial products if b is negative. Convert the two inputs to sign-magnitude notation, multiply unsigned numbers, and convert the result back to 2's complement. Compare the cost and performance (delay) of the two approaches. Select the approach that gives the lowest cost and show its design in terms of basic components (gates, adders, etc.) 2's complement multiplier, implementation. Write Verilog code for your 2's complement multiplier from Exercise 10.50 and demonstrate its correct operation by simulating it on representative test cases

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts